- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4455 > EP4CGX30CF19I7N (Altera)IC CYCLONE IV GX FPGA 30K 324FBG PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉锛� | EP4CGX30CF19I7N |

| 寤犲晢锛� | Altera |

| 鏂囦欢闋佹暩(sh霉)锛� | 35/42闋� |

| 鏂囦欢澶�?銆�?/td> | 0K |

| 鎻忚堪锛� | IC CYCLONE IV GX FPGA 30K 324FBG |

| 鐢�(ch菐n)鍝佸煿瑷�(x霉n)妯″锛� | Cyclone IV FPGA Family Overview |

| 鐗硅壊鐢�(ch菐n)鍝侊細 | Cyclone? IV FPGAs |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 84 |

| 绯诲垪锛� | CYCLONE® IV GX |

| LAB/CLB鏁�(sh霉)锛� | 1840 |

| 閭忚集鍏冧欢/鍠厓鏁�(sh霉)锛� | 29440 |

| RAM 浣嶇附瑷堬細 | 1105920 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 150 |

| 闆绘簮闆诲锛� | 1.16 V ~ 1.24 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | -40°C ~ 100°C |

| 灏佽/澶栨锛� | 324-LBGA |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 324-FBGA锛�19x19锛� |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�鐣�(d膩ng)鍓嶇35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�

1鈥�40

Chapter 1: Cyclone IV Device Datasheet

Glossary

December 2013

Altera Corporation

T

tC

High-speed receiver and transmitter input and output clock period.

Channel-to-

channel-skew

(TCCS)

High-speed I/O block: The timing difference between the fastest and slowest output edges,

including tCO variation and clock skew. The clock is included in the TCCS measurement.

tcin

Delay from the clock pad to the I/O input register.

tCO

Delay from the clock pad to the I/O output.

tcout

Delay from the clock pad to the I/O output register.

tDUTY

High-speed I/O block: Duty cycle on high-speed transmitter output clock.

tFALL

Signal high-to-low transition time (80鈥�20%).

tH

Input register hold time.

Timing Unit

Interval (TUI)

High-speed I/O block: The timing budget allowed for skew, propagation delays, and data

sampling window. (TUI = 1/(Receiver Input Clock Frequency Multiplication Factor) = tC/w).

tINJITTER

Period jitter on the PLL clock input.

tOUTJITTER_DEDCLK

Period jitter on the dedicated clock output driven by a PLL.

tOUTJITTER_IO

Period jitter on the general purpose I/O driven by a PLL.

tpllcin

Delay from the PLL inclk pad to the I/O input register.

tpllcout

Delay from the PLL inclk pad to the I/O output register.

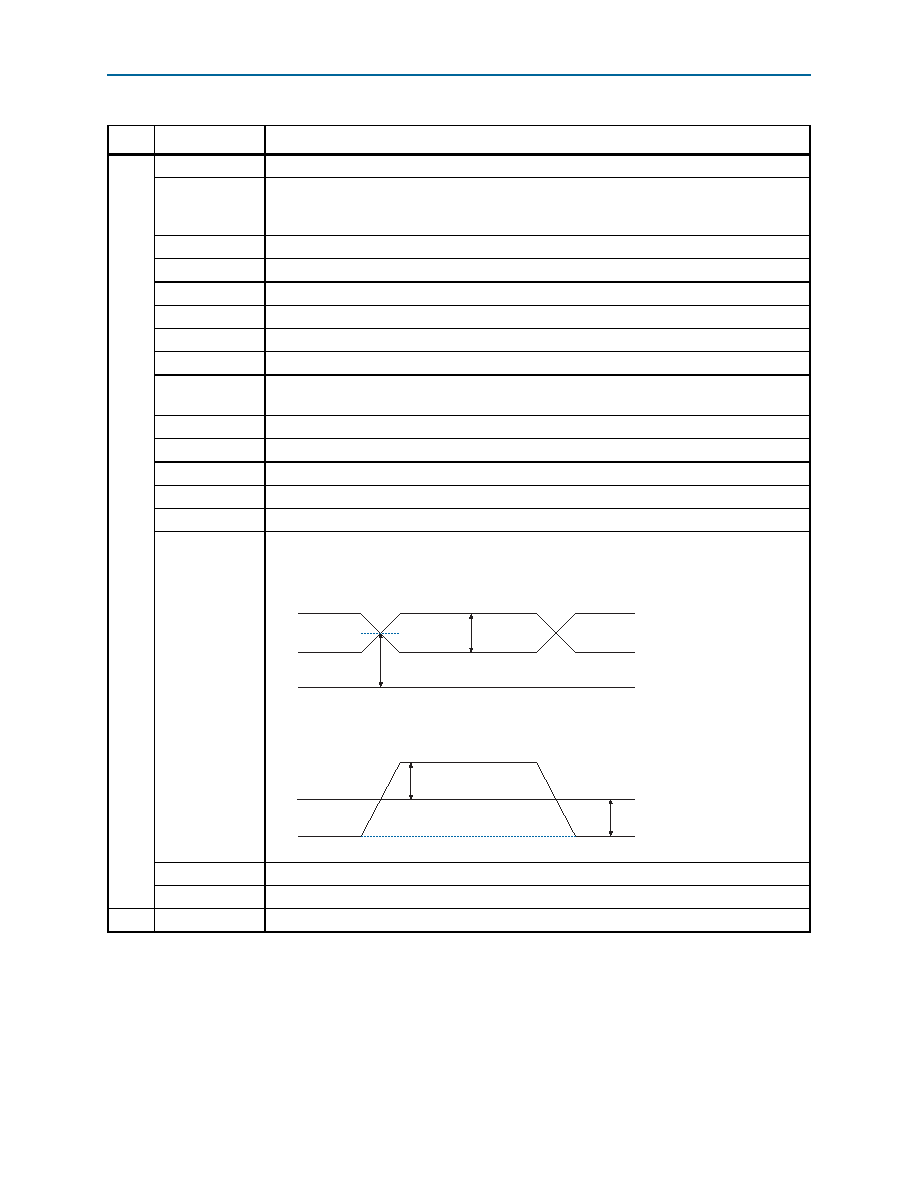

Transmitter

Output

Waveform

Transmitter output waveforms for the LVDS, mini-LVDS, PPDS and RSDS Differential I/O

Standards:

tRISE

Signal low-to-high transition time (20鈥�80%).

tSU

Input register setup time.

U

鈥斺€�

Table 1鈥�46. Glossary (Part 4 of 5)

Letter

Term

Definitions

Single-Ended Waveform

Differential Waveform (Mathematical Function of Positive & Negative Channel)

Positive Channel (p) = V

OH

Negative Channel (n) = V

OL

Ground

VOD

V

OD

V

OD

0 V

Vos

p

- n

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| 5748678-5 | CONN BACKSHELL DB50 PLASTIC BLCK |

| AMM28DRTS | CONN EDGECARD 56POS DIP .156 SLD |

| 5745171-1 | CONN BACKSHELL DB9 DIE CAST |

| ASC43DRTI-S93 | CONN EDGECARD 86POS DIP .100 SLD |

| EP4CGX30CF19C6N | IC CYCLONE IV GX FPGA 30K 324FBG |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| EP4CGX30CF23C6 | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪 FPGA - Cyclone IV GX 1840 LABs 290 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP4CGX30CF23C6N | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪 FPGA - Cyclone IV GX 1840 LABs 290 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP4CGX30CF23C7 | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪 FPGA - Cyclone IV GX 1840 LABs 290 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP4CGX30CF23C7N | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪 FPGA - Cyclone IV GX 1840 LABs 290 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP4CGX30CF23C8 | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪 FPGA - Cyclone IV GX 1840 LABs 290 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

鐧�(f膩)甯冪穵鎬ラ噰璩硷紝3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�