- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19313 > EP4SGX110DF29C3N (Altera)IC STRATIX IV GX 110K 780FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4SGX110DF29C3N |

| 廠商: | Altera |

| 文件頁數(shù): | 79/82頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV GX 110K 780FBGA |

| 產(chǎn)品培訓模塊: | Stratix IV FPGAs Three Reasons to Use FPGA's in Industrial Designs |

| 特色產(chǎn)品: | Stratix? IV Series FPGAs |

| 標準包裝: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB數(shù): | 4224 |

| 邏輯元件/單元數(shù): | 105600 |

| RAM 位總計: | 9793536 |

| 輸入/輸出數(shù): | 372 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 780-BBGA |

| 供應商設備封裝: | 780-FBGA(29x29) |

| 其它名稱: | 544-2630 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當前第79頁第80頁第81頁第82頁

2–2

Chapter 2: Addendum to the Stratix IV Device Handbook

Stratix IV Device Handbook

February 2011

Altera Corporation

Volume 4: Device Datasheet and Addendum

Document Revision History

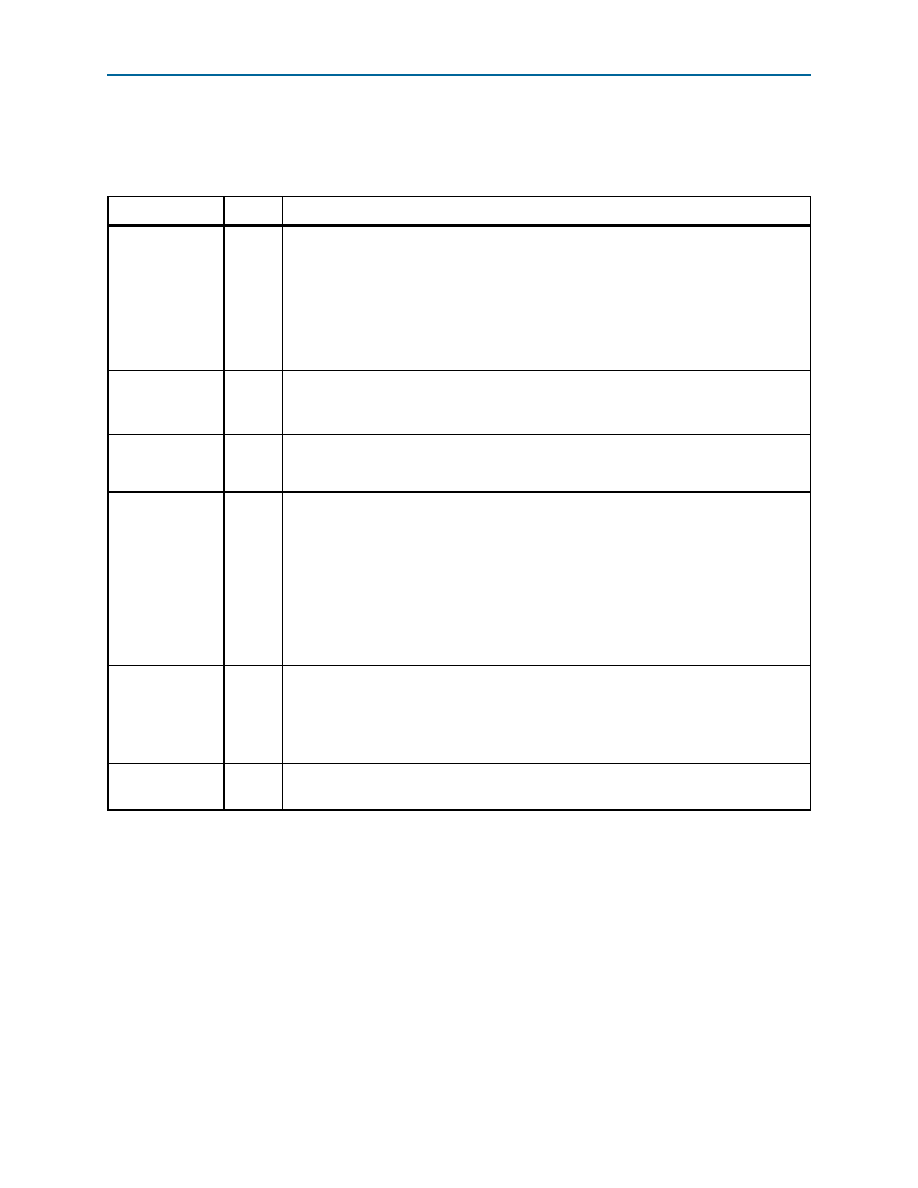

Table 2–1 lists the revision history for this chapter.

Table 2–1. Document Revision History

Date

Version

Changes

February 2011

1.5

■ Removed the “Decision Feedback Equalization (DFE)” section now that AN 612: Decision

Feedback Equalization in Stratix IV Devices is published.

Stratix IV Devices chapter.

■ Moved the “Power-On Reset Circuitry” and “Power-On Reset Specifications” sections to

■ Minor text edits.

September 2010

1.4

■ Added new information for the Decision Feedback Equalization (DFE) feature.

April 2010

1.3

March 2010

1.2

■ Moved the “Power-On Reset Circuitry”, “Power-On Reset Specifications”, “Correct

Power-Up Sequence for Production Devices”, and “Correct Power-Up Sequence for

Production Devices” sections to the Hot Socketing and Power-On Reset in Stratix IV

Devices chapter.

■ Moved the “Power-On Reset Circuit” and “JTAG TMS and TDI Pin Pull-Up Resistor Value

Specification” sections to the Configuration, Design Security, Remote System Upgrades

with Stratix IV Devices chapter.

■ Moved the “Summary of OCT Assignments” section to the I/O Features in Stratix IV

Devices chapter.

February 2010

1.1

■ Added the “Power-On Reset Circuitry”, “Power-On Reset Specifications”, “Correction to

POR Signal Pulse Width Delay Times”, “Correct Power-Up Sequence for Production

Devices”, “Power-On Reset Circuit”, “Summary of OCT Assignments”, and “JTAG TMS

and TDI Pin Pull-Up Resistor Value Specification” sections.

■ Minor text edits.

November 2009

1.0

■ Stratix IV GX enhanced transceiver data rate specifications in

–4 commercial speed grade.

■ Initial release.

相關PDF資料 |

PDF描述 |

|---|---|

| ECM06DCMS | CONN EDGECARD 12POS .156 WW |

| MC79L05ACPX | IC REG LDO -5V .1A TO-92 |

| VI-21W-EU | CONVERTER MOD DC/DC 5.5V 200W |

| TACL335M002RTA | CAP TANT 3.3UF 2V 20% 0603 |

| EP3SL150F1152C3N | IC STRATX III FPGA 150K 1152FBGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP4SGX110DF29C4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110DF29C4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110DF29I3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110DF29I3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110DF29I4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。