- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4181 > EP4SGX230DF29C3ES (Altera)IC STRATIX IV GX 230K 780-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4SGX230DF29C3ES |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 69/82頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC STRATIX IV GX 230K 780-FBGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Stratix® IV GX |

| LAB/CLB數(shù): | 9120 |

| 邏輯元件/單元數(shù): | 228000 |

| RAM 位總計(jì): | 17544192 |

| 輸入/輸出數(shù): | 372 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 780-BBGA |

| 供應(yīng)商設(shè)備封裝: | 780-FBGA(29x29) |

| 配用: | 544-2594-ND - KIT DEVELOPMENT STRATIX IV 544-2592-ND - KIT DEV STRATIX IV 4SGX230N/C2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)當(dāng)前第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

1–63

I/O Timing

March 2014

Altera Corporation

Stratix IV Device Handbook

Volume 4: Device Datasheet and Addendum

Programmable IOE Delay

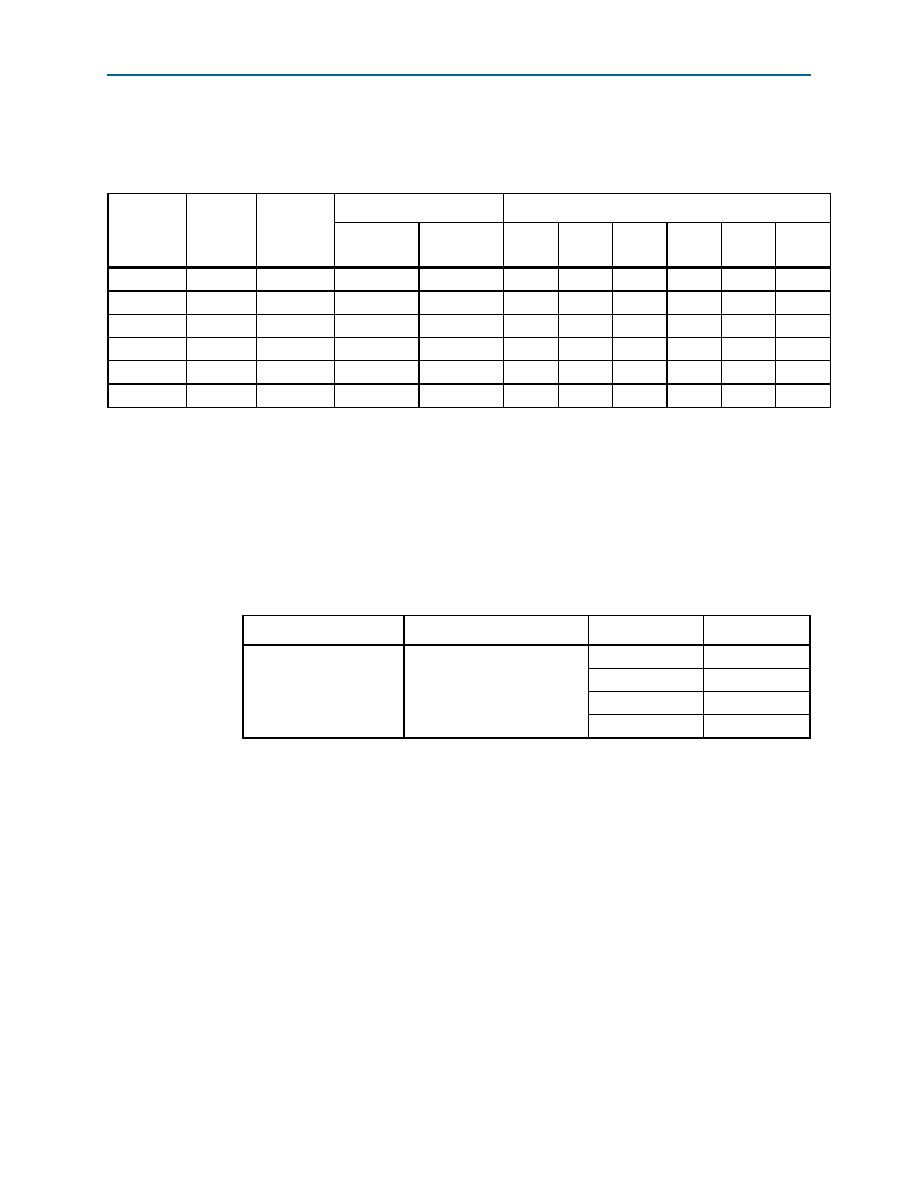

Table 1–52 lists the Stratix IV IOE programmable delay settings.

Programmable Output Buffer Delay

Table 1–53 lists the delay chain settings that control the rising and falling edge delays

of the output buffer. The default delay is 0 ps.

Table 1–52. IOE Programmable Delay for Stratix IV Devices

Parameter

Available

Settings

Min Offset

Fast Model

Slow Model

Industrial/

Military

Commercial

C2 (3)

C3

C4

I3/M3

I4

Unit

D1

16

0

0.462

0.505

0.732

0.795

0.857

0.801

0.864

ns

D2

8

0

0.234

0.232

0.337

0.372

0.407

0.371

0.405

ns

D3

8

0

1.700

1.769

2.695

2.927

3.157

2.948

3.178

ns

D4

16

0

0.508

0.554

0.813

0.882

0.952

0.889

0.959

ns

D5

16

0

0.472

0.500

0.747

0.799

0.875

0.817

0.882

ns

D6

7

0

0.186

0.195

0.294

0.319

0.345

0.321

0.347

ns

Notes to Table 1–52:

(1) You can set this value in the Quartus II software by selecting D1, D2, D3, D4, D5, and D6 in the Assignment Name column.

(2) Minimum offset does not include the intrinsic delay.

(3) For the EP4SGX530 device density, the IOE programmable delays have an additional 5% maximum offset.

Table 1–53. Programmable Output Buffer Delay (1)

Symbol

Parameter

Typical

Unit

DOUTBUF

Rising and/or falling edge

delay

0 (default)

ps

50

ps

100

ps

150

ps

Note to Table 1–53:

(1) You can set the programmable output buffer delay in the Quartus II software by setting the Output Buffer Delay

Control assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the

Output Buffer Delay assignment.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP4SE530H40C3NES | IC STRATIX IV E 530K 1517-HBGA |

| ASM43DTAD-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| EP4SE530H40C3ES | IC STRATIX IV E 530K 1517-HBGA |

| IDT7164S20YGI8 | IC SRAM 64KBIT 20NS 28SOJ |

| EP4SE530H35C3NES | IC STRATIX IV E 530K 1152-HBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4SGX230DF29C3N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV GX 9120 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX230DF29C3NES | 功能描述:IC STRATIX IV GX 230K 780-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Stratix® IV GX 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| EP4SGX230DF29C4 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV GX 9120 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX230DF29C4ES | 制造商:Altera Corporation 功能描述:IC FPGA 372 I/O 780FBGA 制造商:Altera Corporation 功能描述:IC STRATIX IV GX FPGA 780FBGA |

| EP4SGX230DF29C4N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV GX 9120 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。