- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4310 > EP4SGX360FF35C3N (Altera)IC STRATIX IV FPGA 360K 1152FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4SGX360FF35C3N |

| 廠商: | Altera |

| 文件頁數(shù): | 52/82頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 360K 1152FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB數(shù): | 14144 |

| 邏輯元件/單元數(shù): | 353600 |

| RAM 位總計: | 23105536 |

| 輸入/輸出數(shù): | 564 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1152-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1152-FBGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當(dāng)前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

1–48

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

Switching Characteristics

Stratix IV Device Handbook

March 2014

Altera Corporation

Volume 4: Device Datasheet and Addendum

PLL Specifications

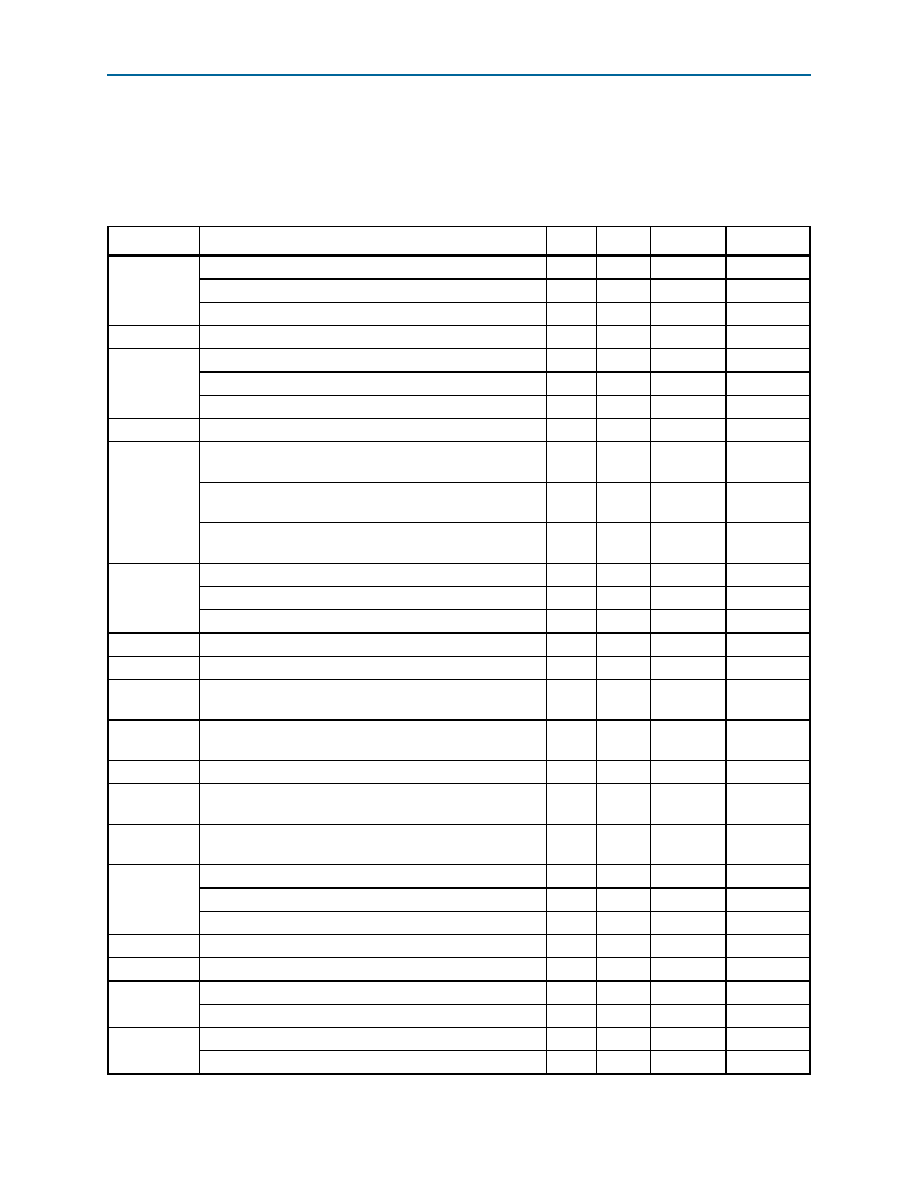

Table 1–34 lists the Stratix IV PLL specifications when operating in the commercial

(0° to 85°C), industrial (–40° to 100°C), and military (–55°C to 125°C) junction

temperature ranges.

Table 1–34. PLL Specifications for Stratix IV Devices (Part 1 of 2)

Symbol

Parameter

Min

Typ

Max

Unit

fIN

Input clock frequency (–2/–2x speed grade)

5

—

800 (1)

MHz

Input clock frequency (–3 speed grade)

5

—

717 (1)

MHz

Input clock frequency (–4 speed grade)

5

—

717 (1)

MHz

fINPFD

Input frequency to the PFD

5

—

325

MHz

fVCO (2)

PLL VCO operating range (–2 speed grade)

600

—

1600

MHz

PLL VCO operating range (–3 speed grade)

600

—

1300

MHz

PLL VCO operating range (–4 speed grade)

600

—

1300

MHz

tEINDUTY

Input clock or external feedback clock input duty cycle

40

—

60

%

fOUT

Output frequency for internal global or regional clock

(–2/–2x speed grade)

—

800 (3)

MHz

Output frequency for internal global or regional clock

(–3 speed grade)

—

717 (3)

MHz

Output frequency for internal global or regional clock

(–4 speed grade)

—

717 (3)

MHz

fOUT_EXT

Output frequency for external clock output (–2 speed grade)

—

800 (3)

MHz

Output frequency for external clock output (–3 speed grade)

—

717 (3)

MHz

Output frequency for external clock output (–4 speed grade)

—

717 (3)

MHz

tOUTDUTY

Duty cycle for external clock output (when set to 50%)

45

50

55

%

tFCOMP

External feedback clock compensation time

—

10

ns

tCONFIGPLL

Time required to reconfigure scan chain

—

3.5

—

scanclk

cycles

tCONFIGPHASE

Time required to reconfigure phase shift

—

1

—

scanclk

cycles

fSCANCLK

scanclk frequency

—

100

MHz

tLOCK

Time required to lock from end-of-device configuration or

de-assertion of areset

——

1

ms

tDLOCK

Time required to lock dynamically (after switchover or

reconfiguring any non-post-scale counters/delays)

——

1

ms

fCLBW

PLL closed-loop low bandwidth

—

0.3

—

MHz

PLL closed-loop medium bandwidth

—

1.5

—

MHz

PLL closed-loop high bandwidth (8)

—4

—

MHz

tPLL_PSERR

Accuracy of PLL phase shift

—

±50

ps

tARESET

Minimum pulse width on the areset signal

10

—

ns

Input clock cycle to cycle jitter (FREF ≥ 100 MHz)

—

0.15

UI (p-p)

Input clock cycle to cycle jitter (FREF < 100 MHz)

—

±750

ps (p-p)

tOUTPJ_DC (6)

Period Jitter for dedicated clock output (FOUT ≥ 100 MHz)

—

175

ps (p-p)

Period Jitter for dedicated clock output (FOUT < 100 MHz)

—

17.5

mUI (p-p)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP4SGX360KF43C4 | IC STRATIX IV FPGA 360K 1760FBGA |

| 170-201-170L003 | CONTACT PIN MALE 30 MICRONS GOLD |

| EP1S80F1508C6 | IC STRATIX FPGA 80K LE 1508-FBGA |

| EP1S80B956C6 | IC STRATIX FPGA 80K LE 956-BGA |

| 24AA08H-I/P | IC EEPROM 8KBIT 400KHZ 8DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4SGX360FF35C4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX360FF35C4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX360FF35I3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX360FF35I3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX360FF35I4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。