Chapter 1: DC and Switching Characteristics for Stratix IV Devices

1–51

Switching Characteristics

March 2014

Altera Corporation

Stratix IV Device Handbook

Volume 4: Device Datasheet and Addendum

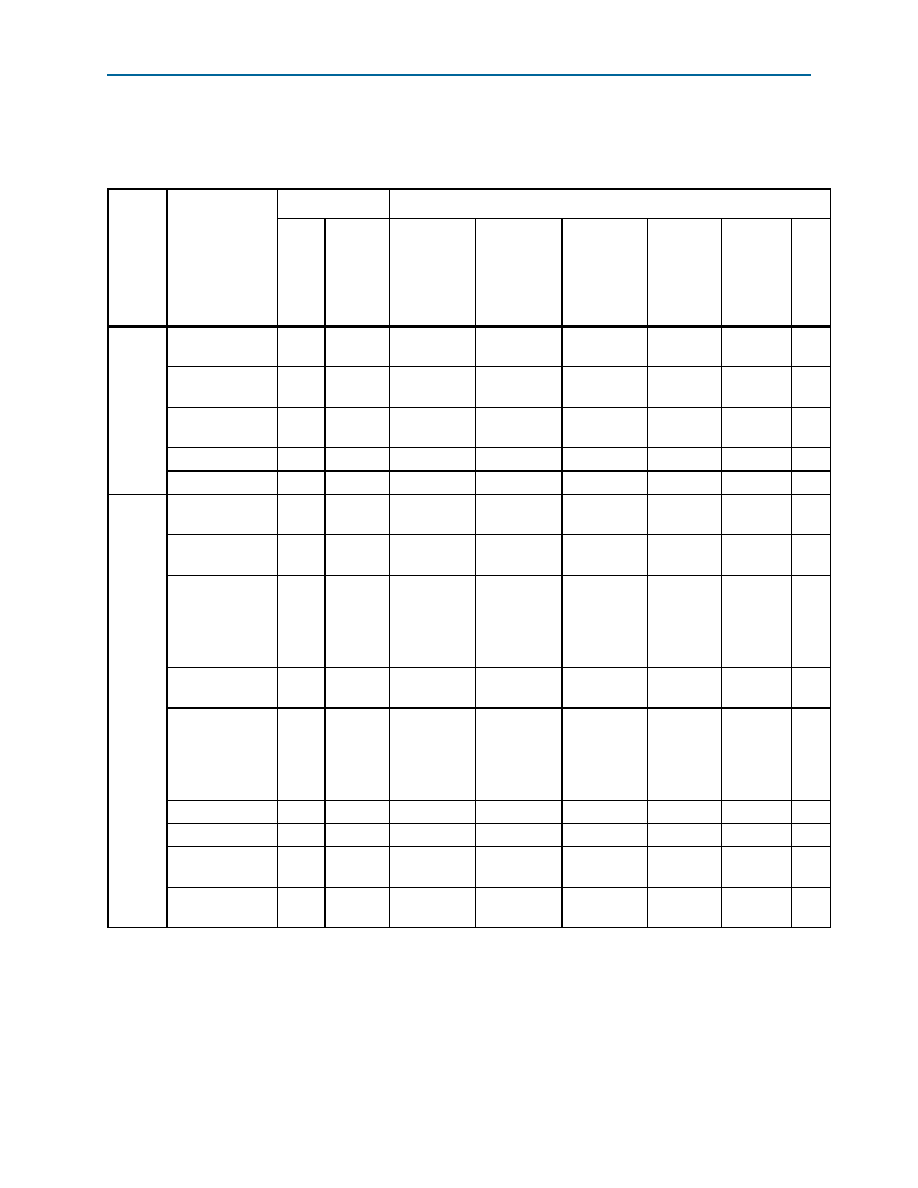

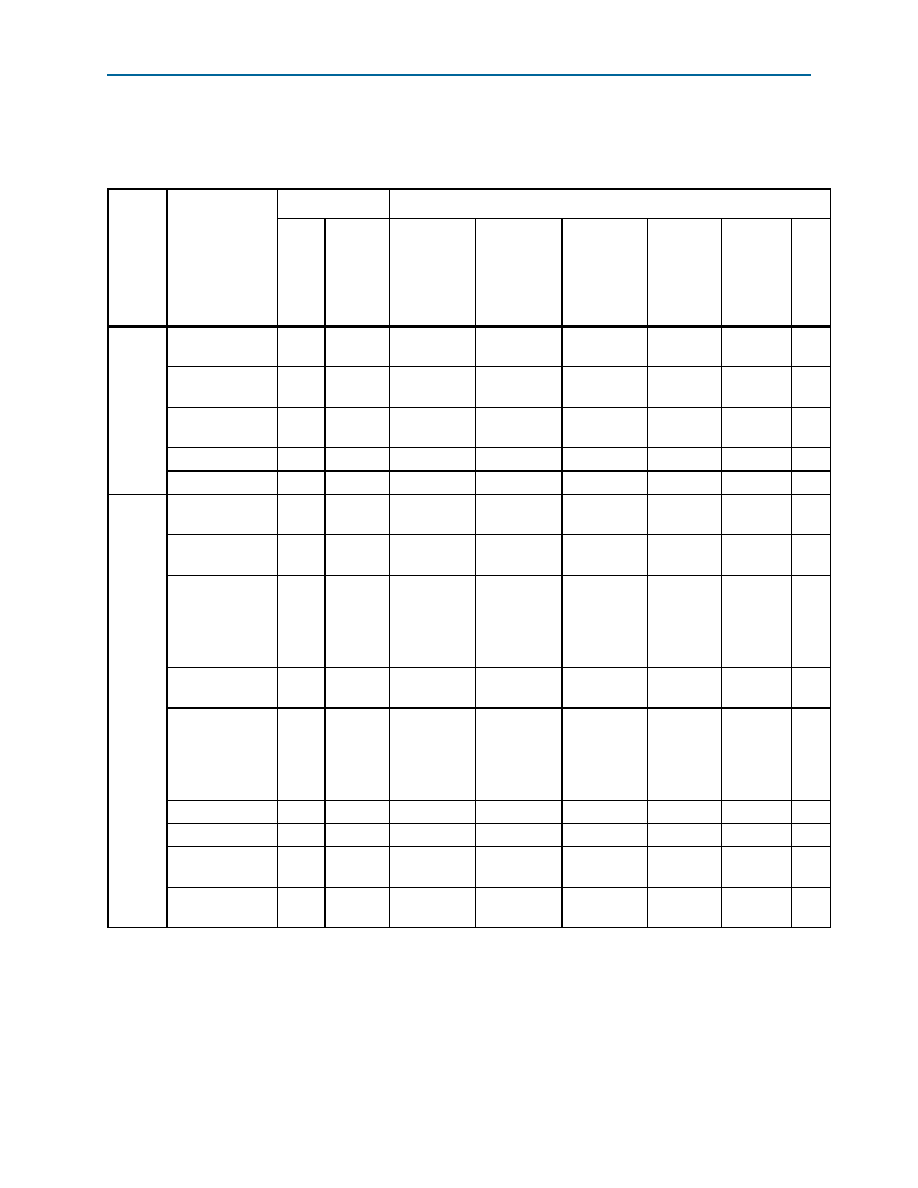

TriMatrix Memory Block Specifications

Table 1–36 lists the Stratix IV TriMatrix memory block specifications.

Table 1–36. TriMatrix Memory Block Performance Specifications for Stratix IV

Devices (1) (Part 1 of 2)

Memory

Mode

Resources Used

Performance

ALUTs

TriMatrix

Memory

–1 Industrial

and –2 /–2×

Commercial/

Industrial

Speed Grade

–3

Commercial/

Industrial/

Military

Speed Grade

–4

Commercial/

Industrial

Speed Grade

–3

Industrial/

Military

Speed

Grade

–4

Industrial

Speed

Grade

Unit

MLAB

Single port

64×10

0

1

600

500

450

500

450

MHz

Simple dual-port

32×20

0

1

600

500

450

500

450

MHz

Simple dual-port

64×10

0

1

600

500

450

500

450

MHz

ROM 64×10

0

1

600

500

450

500

450

MHz

ROM 32×20

0

1

600

500

450

500

450

MHz

M9K

Block

Single-port

256×36

0

1

600

540

475

540

475

MHz

Simple dual-port

256×36

0

1

550

490

420

490

420

MHz

Simple dual-port

256×36, with the

read-during-write

option set to Old

Data

0

1

375

340

300

340

300

MHz

True dual port

512×18

0

1

490

430

370

430

370

MHz

True dual-port

512×18, with the

read-during-write

option set to Old

Data

0

1

375

335

290

335

290

MHz

ROM 1 Port

0

1

600

540

475

540

475

MHz

ROM 2 Port

0

1

600

540

475

540

475

MHz

Min Pulse Width

(clock high time)

—

750

800

850

800

850

ps

Min Pulse Width

(clock low time)

—

500

625

690

625

690

ps