參數資料

| 型號: | EP4SGX530KF43C2N |

| 廠商: | Altera |

| 文件頁數: | 37/82頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 530K 1760FBGA |

| 產品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB數: | 21248 |

| 邏輯元件/單元數: | 531200 |

| RAM 位總計: | 28033024 |

| 輸入/輸出數: | 880 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1760-BBGA,FCBGA |

| 供應商設備封裝: | 1760-FCBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

1–34

Switching Characteristics

March 2014

Altera Corporation

Stratix IV Device Handbook

Volume 4: Device Datasheet and Addendum

Stratix IV GX and GT devices.

Table 1–29 lists typical transmitter pre-emphasis levels in dB for the first post tap

under the following conditions (low-frequency data pattern [five 1s and five 0s] at

6.25 Gbps). The levels listed in Table 1–29 are a representation of possible

pre-emphasis levels under the specified conditions only and that the pre-emphasis

levels may change with data pattern and data rate.

f To predict the pre-emphasis level for your specific data rate and pattern, run

simulations using the Stratix IV HSSI HSPICE models.

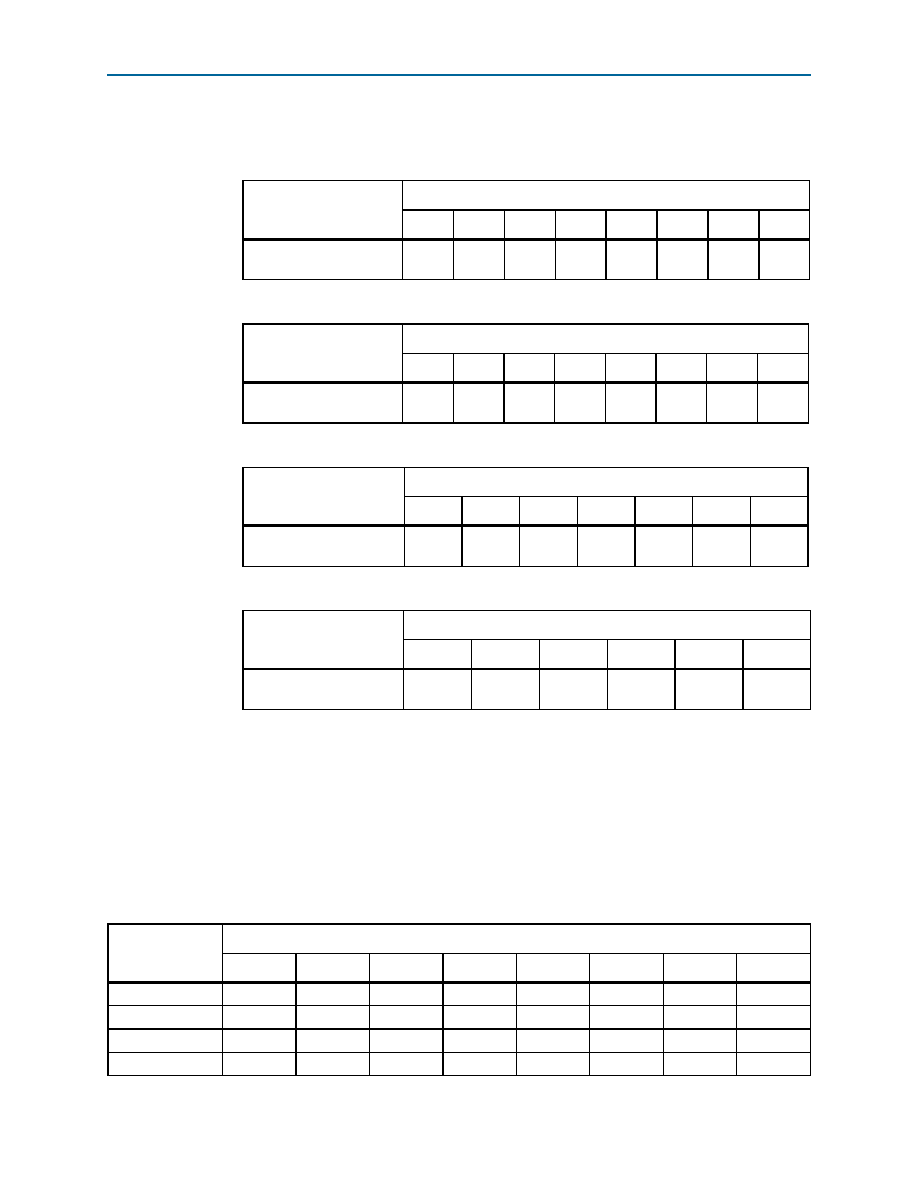

Table 1–25. Typical VOD Setting, TX Term = 85

Symbol

VOD Setting (mV)

0

123

45

67

VOD differential

peak-to-peak Typical (mV)

170 ±

20%

340 ±

20%

510 ±

20%

595 ±

20%

680 ±

20%

765 ±

20%

850 ±

20%

1020 ±

20%

Table 1–26. Typical VOD Setting, TX Term = 100

Symbol

VOD Setting (mV)

012

34

567

VOD differential

peak-to-peak Typical (mV)

200 ±

20%

400 ±

20%

600 ±

20%

700 ±

20%

800 ±

20%

900 ±

20%

1000

± 20%

1200

± 20%

Table 1–27. Typical VOD Setting, TX Term = 120

Symbol

VOD Setting (mV)

0123456

VOD differential

peak-to-peak Typical (mV)

240 ±

20%

480 ±

20%

720 ±

20%

840 ±

20%

960 ±

20%

1080 ±

20%

1200 ±

20%

Table 1–28. Typical VOD Setting, TX Term = 150

Symbol

VOD Setting (mV)

01

23

45

VOD differential

peak-to-peak Typical (mV)

300 ±

20%

600 ±

20%

900 ±

20%

1050 ±

20%

1200 ±

20%

1350 ±

20%

Table 1–29. Transmitter Pre-Emphasis Levels for Stratix IV Devices (Part 1 of 2)

Pre-Emphasis 1st

Post-Tap Setting

VOD Setting

0

123

4567

0

000

0000

1

N/A

0.7

00

0000

2

N/A

1

0.3

0

0000

3

N/A

1.5

0.6

0

0000

相關PDF資料 |

PDF描述 |

|---|---|

| RSC65DRYN | CONN EDGECARD 130PS DIP .100 SLD |

| RMC65DRYN | CONN EDGECARD 130PS DIP .100 SLD |

| RSC65DRYH | CONN EDGECARD 130PS DIP .100 SLD |

| 34VL02T/SN | IC EEPROM 2KBIT 400KHZ 8SOIC |

| 34VL02/SN | IC EEPROM 2KBIT 400KHZ 8SOIC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EP4SGX530KF43C3 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Stratix IV GX 21248 LABs 880 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX530KF43C3N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Stratix IV GX 21248 LABs 880 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX530KF43C4 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Stratix IV GX 21248 LABs 880 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX530KF43C4N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Stratix IV GX 21248 LABs 880 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX530KF43I3 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Stratix IV GX 21248 LABs 880 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。