- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19851 > EPM3128ATC100-10N (Altera)IC MAX 3000A CPLD 128 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | EPM3128ATC100-10N |

| 廠商: | Altera |

| 文件頁數(shù): | 17/46頁 |

| 文件大小: | 0K |

| 描述: | IC MAX 3000A CPLD 128 100-TQFP |

| 產(chǎn)品變化通告: | Bond Wire Change 4/Sept/2008 |

| 標(biāo)準(zhǔn)包裝: | 270 |

| 系列: | MAX® 3000A |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 10.0ns |

| 電壓電源 - 內(nèi)部: | 3 V ~ 3.6 V |

| 邏輯元件/邏輯塊數(shù)目: | 8 |

| 宏單元數(shù): | 128 |

| 門數(shù): | 2500 |

| 輸入/輸出數(shù): | 80 |

| 工作溫度: | 0°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 603 (CN2011-ZH PDF) |

| 其它名稱: | 544-1981 EPM3128ATC100-10N-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

24

Altera Corporation

MAX 3000A Programmable Logic Device Family Data Sheet

Notes to tables:

(1)

(2)

Minimum DC input voltage is –0.5 V. During transitions, the inputs may undershoot to –2.0 V or overshoot to

5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

(3)

All pins, including dedicated inputs, I/O pins, and JTAG pins, may be driven before VCCINT and VCCIO are

powered.

(4)

These values are specified under the recommended operating conditions, as shown in Table 13 on page 23.

(5)

The parameter is measured with 50% of the outputs each sourcing the specified current. The IOH parameter refers

to high–level TTL or CMOS output current.

(6)

The parameter is measured with 50% of the outputs each sinking the specified current. The IOL parameter refers to

low–level TTL, PCI, or CMOS output current.

(7)

This value is specified during normal device operation. During power-up, the maximum leakage current is

±300

μA.

(8)

This pull–up exists while devices are programmed in–system and in unprogrammed devices during power–up.

(9)

Capacitance is measured at 25

° C and is sample–tested only. The OE1 pin (high–voltage pin during programming)

has a maximum capacitance of 20 pF.

(10) The POR time for all MAX 3000A devices does not exceed 100

μs. The sufficient VCCINT voltage level for POR is

3.0 V. The device is fully initialized within the POR time after VCCINT reaches the sufficient POR voltage level.

(11) These devices support in-system programming for –40° to 100° C. For in-system programming support between –40°

and 0° C, contact Altera Applications.

Figure 9 shows the typical output drive characteristics of MAX 3000A

devices.

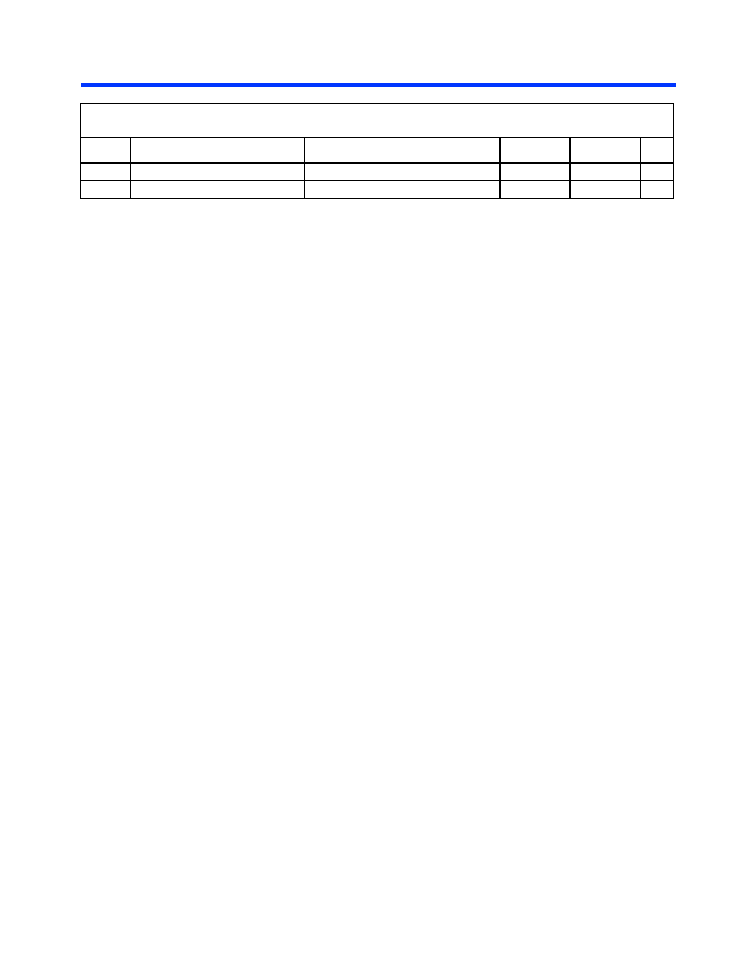

Table 15. MAX 3000A Device Capacitance

Symbol

Parameter

Conditions

Min

Max

Unit

CIN

Input pin capacitance

VIN = 0 V, f = 1.0 MHz

8

pF

CI/O

I/O pin capacitance

VOUT = 0 V, f = 1.0 MHz

8

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EMM40DRMN-S288 | CONN EDGECARD 80POS .156 EXTEND |

| EPM240F100I5N | IC MAX II CPLD 240 LE 100-FBGA |

| EPM240F100C4N | IC MAX II CPLD 240 LE 100-FBGA |

| TIM106M025P0Y | CAP TANT 10UF 25V 20% RADIAL |

| EPM7064SLC44-10 | IC MAX 7000 CPLD 64 44-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM3128ATC100-5 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 128 Macro 80 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3128ATC100-5N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 128 Macro 80 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3128ATC100-7 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 128 Macro 80 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3128ATC100-7N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 128 Macro 80 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3128ATC144-10 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 128 Macro 96 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。