- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨�(m菐i)璩�(m脿i)IC缍�(w菐ng) > PDF鐩寗19556 > EPM7064STC100-10F (Altera)IC MAX 7000 CPLD 64 100-TQFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | EPM7064STC100-10F |

| 寤犲晢锛� | Altera |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 42/66闋�(y猫) |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC MAX 7000 CPLD 64 100-TQFP |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 270 |

| 绯诲垪锛� | MAX® 7000 |

| 鍙法绋嬮(l猫i)鍨嬶細 | 绯荤当(t菕ng)鍏�(n猫i)鍙法绋� |

| 鏈€澶у欢閬叉檪(sh铆)闁� tpd(1)锛� | 10.0ns |

| 闆诲闆绘簮 - 鍏�(n猫i)閮細 | 4.75 V ~ 5.25 V |

| 閭忚集鍏冧欢/閭忚集濉婃暩(sh霉)鐩細 | 4 |

| 瀹忓柈鍏冩暩(sh霉)锛� | 64 |

| 闁€(m茅n)鏁�(sh霉)锛� | 1250 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 68 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 瀹夎椤�(l猫i)鍨嬶細 | 琛ㄩ潰璨艰 |

| 灏佽/澶栨锛� | 100-TQFP |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 100-TQFP锛�14x14锛� |

| 鍖呰锛� | 鎵樼洡(p谩n) |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)鐣�(d膩ng)鍓嶇42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)绗�61闋�(y猫)绗�62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)

Altera Corporation

47

MAX 7000 Programmable Logic Device Family Data Sheet

tACNT

Minimum array clock period

6.7

8.2

10.0

13.0

ns

fACNT

Maximum internal array clock

frequency

149.3

122.0

100.0

76.9

MHz

fMAX

Maximum clock frequency

166.7

125.0

100.0

MHz

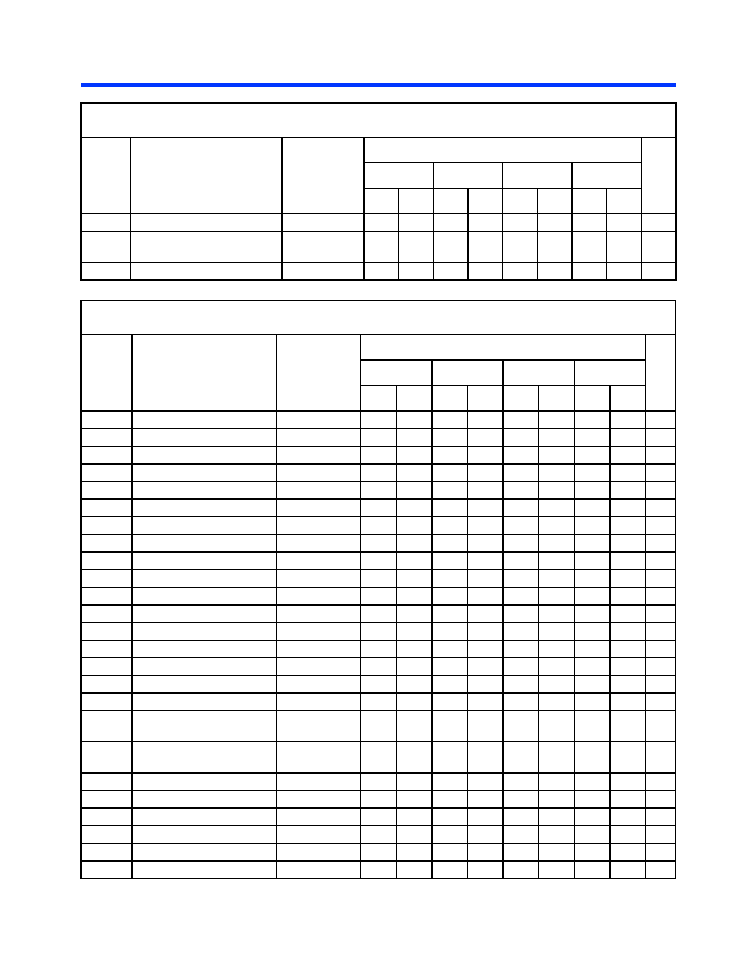

Table 34. EPM7160S Internal Timing Parameters (Part 1 of 2)

Symbol

Parameter

Conditions

Speed Grade

Unit

-6

-7

-10

-15

Min

Max

Min

Max

Min

Max

Min

Max

tIN

Input pad and buffer delay

0.2

0.3

0.5

2.0

ns

tIO

I/O input pad and buffer delay

0.2

0.3

0.5

2.0

ns

tFIN

Fast input delay

2.6

3.2

1.0

2.0

ns

tSEXP

Shared expander delay

3.6

4.3

5.0

8.0

ns

tPEXP

Parallel expander delay

1.0

1.3

0.8

1.0

ns

tLAD

Logic array delay

2.8

3.4

5.0

6.0

ns

tLAC

Logic control array delay

2.8

3.4

5.0

6.0

ns

tIOE

Internal output enable delay

0.7

0.9

2.0

3.0

ns

tOD1

Output buffer and pad delay

C1 = 35 pF

0.4

0.5

1.5

4.0

ns

tOD2

Output buffer and pad delay

C1 = 35 pF (6)

0.9

1.0

2.0

5.0

ns

tOD3

Output buffer and pad delay

C1 = 35 pF

5.4

5.5

8.0

ns

tZX1

Output buffer enable delay

C1 = 35 pF

4.0

5.0

6.0

ns

tZX2

Output buffer enable delay

C1 = 35 pF (6)

4.5

5.5

7.0

ns

tZX3

Output buffer enable delay

C1 = 35 pF

9.0

10.0

ns

tXZ

Output buffer disable delay

C1 = 5 pF

4.0

5.0

6.0

ns

tSU

Register setup time

1.0

1.2

2.0

4.0

ns

tH

Register hold time

1.6

2.0

3.0

4.0

ns

tFSU

Register setup time of fast

input

1.9

2.2

3.0

2.0

ns

tFH

Register hold time of fast

input

0.6

0.8

0.5

1.0

ns

tRD

Register delay

1.3

1.6

2.0

1.0

ns

tCOMB

Combinatorial delay

1.0

1.3

2.0

1.0

ns

tIC

Array clock delay

2.9

3.5

5.0

6.0

ns

tEN

Register enable time

2.8

3.4

5.0

6.0

ns

tGLOB

Global control delay

2.0

2.4

1.0

ns

tPRE

Register preset time

2.4

3.0

4.0

ns

Table 33. EPM7160S External Timing Parameters (Part 2 of 2)

Note (1)

Symbol

Parameter

Conditions

Speed Grade

Unit

-6

-7

-10

-15

MinMax MinMax MinMax MinMax

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| VI-2TK-CY-F1 | CONVERTER MOD DC/DC 40V 50W |

| VI-B4L-CX-B1 | CONVERTER MOD DC/DC 28V 75W |

| EBM02DSEN-S243 | CONN EDGECARD 4POS .156 EYELET |

| EBC07DRXN-S734 | CONN EDGECARD 14POS DIP .100 SLD |

| TAJD106M016RNJ | CAP TANT 10UF 16V 20% 2917 |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| EPM7064STC100-10FN | 鍔熻兘鎻忚堪:CPLD - 寰�(f霉)闆滃彲绶ㄧ▼閭忚集鍣ㄤ欢 CPLD - MAX 7000 64 Macro 68 IOs RoHS:鍚� 鍒堕€犲晢:Lattice 绯诲垪: 瀛樺劜(ch菙)椤�(l猫i)鍨�:EEPROM 澶ч浕姹�?c谩i)?sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:333 MHz 寤堕伈鏅�(sh铆)闁�:2.7 ns 鍙法绋嬭几鍏�/杓稿嚭绔暩(sh霉)閲�:64 宸ヤ綔闆绘簮闆诲:3.3 V 鏈€澶у伐浣滄韩搴�:+ 90 C 鏈€灏忓伐浣滄韩搴�:0 C 灏佽 / 绠遍珨:TQFP-100 |

| EPM7064STC100-10N | 鍔熻兘鎻忚堪:CPLD - 寰�(f霉)闆滃彲绶ㄧ▼閭忚集鍣ㄤ欢 CPLD - MAX 7000 64 Macro 68 IOs RoHS:鍚� 鍒堕€犲晢:Lattice 绯诲垪: 瀛樺劜(ch菙)椤�(l猫i)鍨�:EEPROM 澶ч浕姹�?c谩i)?sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:333 MHz 寤堕伈鏅�(sh铆)闁�:2.7 ns 鍙法绋嬭几鍏�/杓稿嚭绔暩(sh霉)閲�:64 宸ヤ綔闆绘簮闆诲:3.3 V 鏈€澶у伐浣滄韩搴�:+ 90 C 鏈€灏忓伐浣滄韩搴�:0 C 灏佽 / 绠遍珨:TQFP-100 |

| EPM7064STC100-10N | 鍒堕€犲晢:Altera Corporation 鍔熻兘鎻忚堪:MAX ISP PLD 7064 TQFP100 3.3V |

| EPM7064STC100-5 | 鍔熻兘鎻忚堪:CPLD - 寰�(f霉)闆滃彲绶ㄧ▼閭忚集鍣ㄤ欢 CPLD - MAX 7000 64 Macro 68 IOs RoHS:鍚� 鍒堕€犲晢:Lattice 绯诲垪: 瀛樺劜(ch菙)椤�(l猫i)鍨�:EEPROM 澶ч浕姹�?c谩i)?sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:333 MHz 寤堕伈鏅�(sh铆)闁�:2.7 ns 鍙法绋嬭几鍏�/杓稿嚭绔暩(sh霉)閲�:64 宸ヤ綔闆绘簮闆诲:3.3 V 鏈€澶у伐浣滄韩搴�:+ 90 C 鏈€灏忓伐浣滄韩搴�:0 C 灏佽 / 绠遍珨:TQFP-100 |

| EPM7064STC100-5F | 鍔熻兘鎻忚堪:IC MAX 7000 CPLD 64 100-TQFP RoHS:鍚� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - CPLD锛堝京(f霉)闆滃彲绶ㄧ▼閭忚集鍣ㄤ欢锛� 绯诲垪:MAX® 7000 妯�(bi膩o)婧�(zh菙n)鍖呰:24 绯诲垪:CoolRunner II 鍙法绋嬮(l猫i)鍨�:绯荤当(t菕ng)鍏�(n猫i)鍙法绋� 鏈€澶у欢閬叉檪(sh铆)闁� tpd(1):7.1ns 闆诲闆绘簮 - 鍏�(n猫i)閮�:1.7 V ~ 1.9 V 閭忚集鍏冧欢/閭忚集濉婃暩(sh霉)鐩�:24 瀹忓柈鍏冩暩(sh霉):384 闁€(m茅n)鏁�(sh霉):9000 杓稿叆/杓稿嚭鏁�(sh霉):173 宸ヤ綔婧害:0°C ~ 70°C 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 灏佽/澶栨:208-BFQFP 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:208-PQFP锛�28x28锛� 鍖呰:鎵樼洡(p谩n) |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�