- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19837 > EPM7192SQC160-7 (Altera)IC MAX 7000 CPLD 192 160-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EPM7192SQC160-7 |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 2/66頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 192 160-PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | MAX® 7000 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 7.5ns |

| 電壓電源 - 內(nèi)部: | 4.75 V ~ 5.25 V |

| 邏輯元件/邏輯塊數(shù)目: | 12 |

| 宏單元數(shù): | 192 |

| 門數(shù): | 3750 |

| 輸入/輸出數(shù): | 124 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 160-BQFP |

| 供應(yīng)商設(shè)備封裝: | 160-PQFP(28x28) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 604 (CN2011-ZH PDF) |

| 其它名稱: | 544-2342 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

10

Altera Corporation

MAX 7000 Programmable Logic Device Family Data Sheet

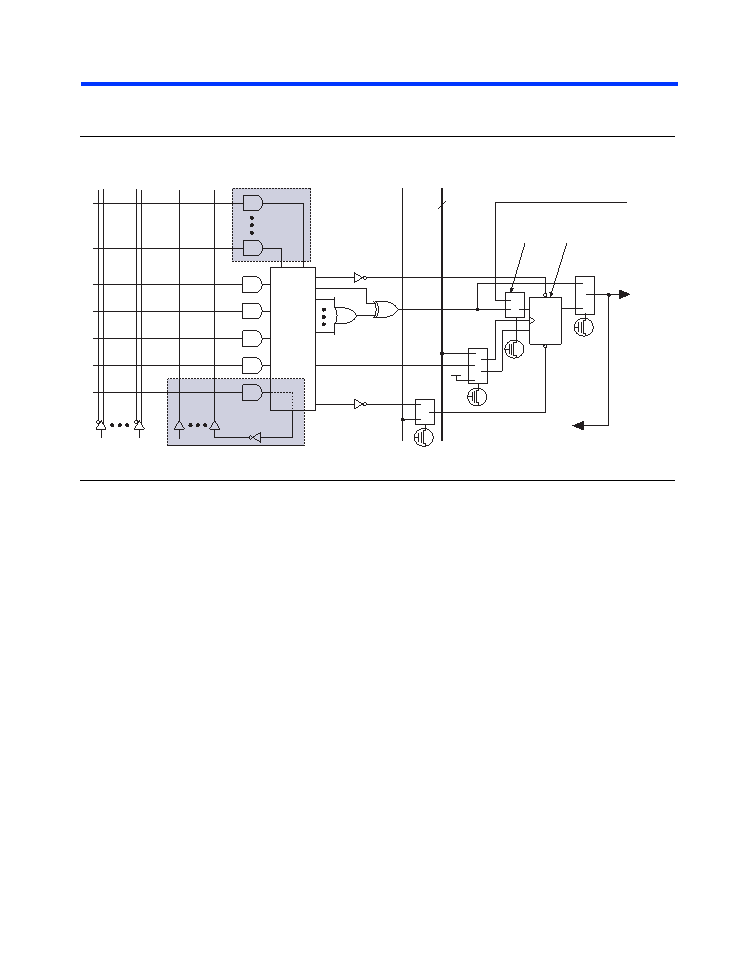

Figure 4 shows a MAX 7000E and MAX 7000S device macrocell.

Figure 4. MAX 7000E & MAX 7000S Device Macrocell

Combinatorial logic is implemented in the logic array, which provides

five product terms per macrocell. The product-term select matrix allocates

these product terms for use as either primary logic inputs (to the OR and

XOR

gates) to implement combinatorial functions, or as secondary inputs

to the macrocell’s register clear, preset, clock, and clock enable control

functions. Two kinds of expander product terms (“expanders”) are

available to supplement macrocell logic resources:

■

Shareable expanders, which are inverted product terms that are fed

back into the logic array

■

Parallel expanders, which are product terms borrowed from adjacent

macrocells

The Altera development system automatically optimizes product-term

allocation according to the logic requirements of the design.

For registered functions, each macrocell flipflop can be individually

programmed to implement D, T, JK, or SR operation with programmable

clock control. The flipflop can be bypassed for combinatorial operation.

During design entry, the designer specifies the desired flipflop type; the

Altera development software then selects the most efficient flipflop

operation for each registered function to optimize resource utilization.

Product-

Term

Select

Matrix

36 Signals

from PIA

16 Expander

Product Terms

Logic Array

Parallel Logic

Expanders

(from other

macrocells)

Shared Logic

Expanders

Clear

Select

Global

Clear

Global

Clocks

Clock/

Enable

Select

2

PRN

CLRN

D/T

Q

ENA

Register

Bypass

to I/O

Control

Block

to PIA

Programmable

Register

from

I/O pin

Fast Input

Select

VCC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISL61851DCBZ | IC USB PWR CTRLR DUAL 8SOIC |

| VI-2WW-CY-F1 | CONVERTER MOD DC/DC 5.5V 50W |

| LCMXO640C-3B256I | IC PLD 640LUTS 159I/O 256-BGA |

| LTC1645CS#TRPBF | IC CTRLR SEQ HOTSWAP DUAL 14SOIC |

| VI-2WW-CY-F3 | CONVERTER MOD DC/DC 5.5V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7192SQC160-7F | 功能描述:IC MAX 7000 CPLD 192 160-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:MAX® 7000 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤 |

| EPM7192SQC160-7N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 192 Macro 124 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7192SQI160-10 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 192 Macro 124 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7192SQI160-10N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 192 Macro 124 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。