- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44220 > FM1901-7RD1HF 1-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE PDF資料下載

參數(shù)資料

| 型號(hào): | FM1901-7RD1HF |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

| 封裝: | METAL, CASE M02, MODULE |

| 文件頁(yè)數(shù): | 16/25頁(yè) |

| 文件大?。?/td> | 569K |

| 代理商: | FM1901-7RD1HF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

Cassette Style

DC-DC Converters

M Series

Edition 01/01.2001

23/25

V ACFAIL Signal (VME)

Available for units with

Uo1 = 5.1 V. This option defines an

undervoltage monitoring circuit for the input or the input and

main output voltage equivalent to option D and generates

the ACFAIL signal (V signal) which conforms to the VME

standard. The low state level of the ACFAIL signal is speci-

fied at a sink current of

IV = 48 mA to UV

≤ 0.6 V (open-col-

lector output of a NPN transistor). The pull-up resistor feed-

ing the open-collector output should be placed on the VME

backplane.

After the ACFAIL signal has gone low, the VME standard

requires a hold-up time

th of at least 4 ms before the 5.1 V

output drops to 4.875 V when the 5.1 V output is fully

loaded. This hold-up time

th is provided by the internal input

capacitance. Consequently the working input voltage and

the threshold level

Uti should be adequately above the mini-

mum input voltage

Uimin of the converter so that enough

energy is remaining in the input capacitance. If the input

voltage is below the required level, an external hold-up ca-

pacitor (

Ci ext) should be added.

Formula for threshold level for desired value of

th:

2

Po (th + 0.3 ms) 100

Uti =

––––––––––––––––––––– +

Ui min2

Ci min

η

V output (V0, V2, V3):

Connector pin V is internally connected to the open collec-

tor of a NPN transistor. The emitter is connected to the

negative potential of output 1.

UV

≤ 0.6 V (logic low) corre-

sponds to a monitored voltage level (

Ui and/or Uo1) < Ut.

The current

IV through the open collector should not exceed

50 mA. The NPN output is not protected against external

overvoltages.

UV should not exceed 80 V.

Ui, Uo1 status

V output,

UV

Ui or Uo1 < Ut

low, L,

UV ≤ 0.6 V at IV = 50 mA

Ui and Uo1 > Ut + Uh

high, H,

I V ≤ 25 A at UV = 5.1 V

Vo1+

Vo1–

V

UV

IV

Rp

Input

11009

voltage(s) exceed(s)

Ut + Uh. The threshold level Ut is either

adjustable by a potentiometer, accessible through a hole in

the front cover, or is factory adjusted to a determined cus-

tomer specified value.

Versions V0, V2 and V3 are available as shown below.

Option V operates independently of the built-in input under-

voltage lock-out circuit. A logic "low" signal is generated at

pin 5 as soon as one of the monitored voltages drops below

the preselected threshold level

Ut. The return for this signal

is Vo1– (pin 23). The V output recovers when the monitored

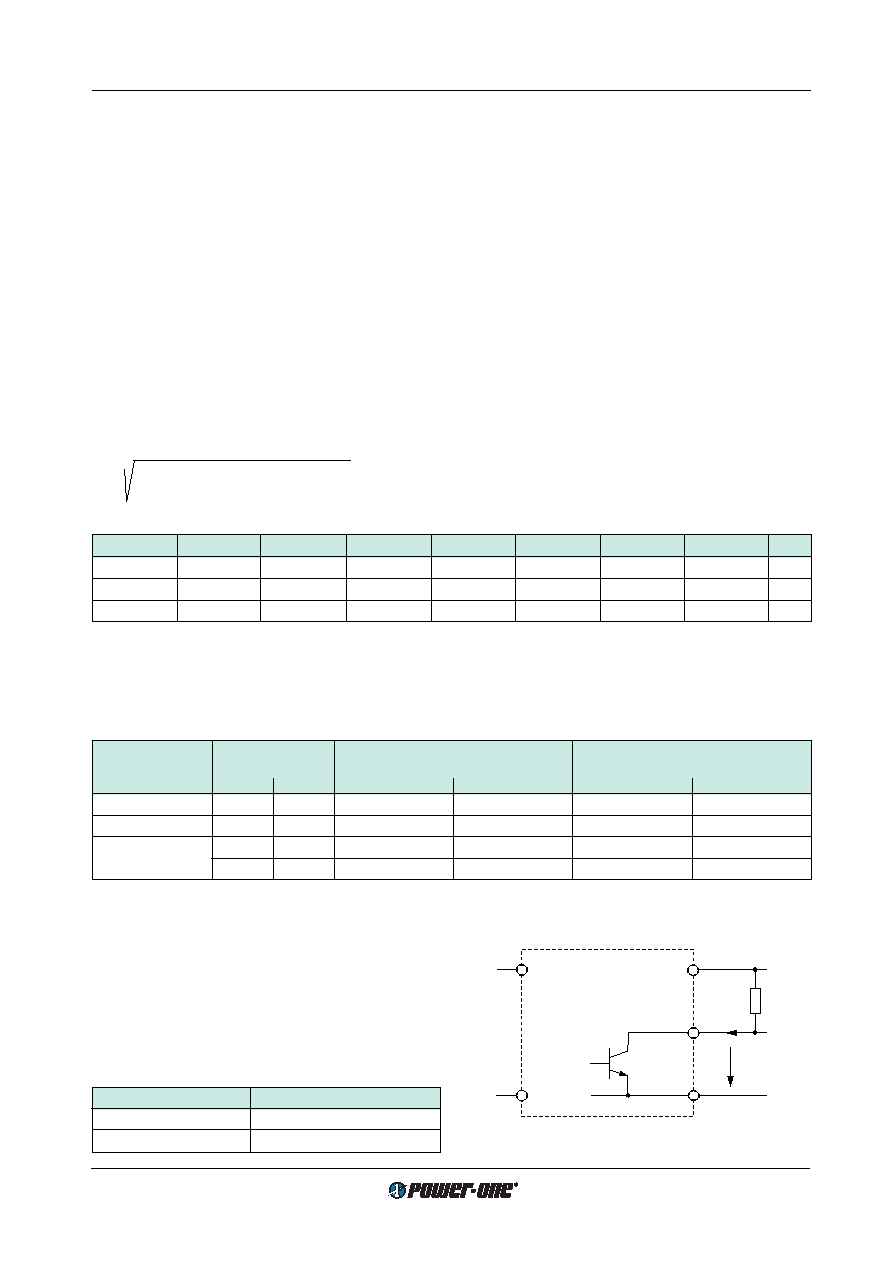

Table 22: Undervoltage monitor functions

V output

Monitoring

Minimum adjustment range

Typical hysteresis

Uh [% of Ut]

(VME compatible)

of threshold level

Ut

for

Ut min...Ut max

Ui

Uo1

Uti

Uto

Uhi

Uho

V2

yes

no

Ui min...Ui max 1

–

3.0...0.5

-

V3

yes

Ui min...Ui max 1

0.95...0.98

Uo1 2

3.0...0.5

"0"

V0

yes

no

Ui min...Ui max 3 4

-

2.2...0.4

-

yes

Ui min...Ui max 3 4

0.95...0.98

Uo1 2

2.2...0.4

"0"

1 Threshold level adjustable by potentiometer (not recommended for mobile applications). 2 Fixed value between 95% and 98% of Uo1

(tracking), output undervoltage monitoring is not a requirement of VME standard. 3 Adjusted at

Io nom.

4 Fixed value, resistor-adjusted (

±2% at 25°C) acc. to customer's specifications; individual type number is determined by Power-One.

Table 21: Available internal input capacitance and factory potentiometer setting of Ut i with resulting hold-up time

Types

AM

BM

CM/CMZ

DM/DMZ

EM

FM

LM/LMZ

Unit

Ci min

2.6

0.67

0.37

0.14

0.37

0.14

mF

Ut i

9.5

19.5

39

61

104

39

120

V DC

th

0.34

0.69

1.92

1.73

6.69

2.92

8.18

ms

Fig. 25

Output configuration of options V0, V2 and V3

Formula for additional external input capacitor

2

Po (th + 0.3 ms) 100

Ci ext = ––––––––––––––––––––– – Ci min

η (U

ti

2 – Ui min2)

where as:

Ci min = minimum internal input capacitance [mF], accord-

ing to the table below

Ci ext = external input capacitance [mF]

Po

= output power [W]

η

= efficiency [%]

th

= hold-up time [ms]

Ui min = minimum input voltage [V]

Uti

= threshold level [V]

Remarks: The threshold level

Uti of option V2 and V3 is ad-

justed during manufacture to a value according to the table

below. A decoupling diode should be connected in series

with the input of AM, BM, CM, DM and FM converters to

avoid the input capacitance discharging through other

loads connected to the same source voltage. If LM or LMZ

units are AC powered, an external input capacitor cannot

be applied unless an additional rectifier is provided.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM1901-7RD7H | 1-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

| FM1901-9PD4AF | 1-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

| FM1901-9RD5AHF | 1-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

| FM2320-7PV2 | 2-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

| FM2320-7PV3HF | 2-OUTPUT 50 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM1901-9R | 制造商:Power-One 功能描述:DCDC - Bulk |

| FM1AB-14SD-A-AA-15HU | 制造商:Hirose 功能描述: |

| FM1AB-14SD-A-AA-160HU | 制造商:Hirose 功能描述: |

| FM1AB-14SD-A-AA-18.0HU | 制造商:Hirose 功能描述:220-1751-0 EACH |

| FM1AB-14SD-A-AA-30HU | 制造商:Hirose 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。