- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375843 > FM24C05UFLZN (FAIRCHILD SEMICONDUCTOR CORP) I2C Serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | FM24C05UFLZN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | I2C Serial EEPROM |

| 中文描述: | 512 X 8 I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| 封裝: | PLASTIC, DIP-8 |

| 文件頁(yè)數(shù): | 8/14頁(yè) |

| 文件大小: | 105K |

| 代理商: | FM24C05UFLZN |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

8

www.fairchildsemi.com

FM24C04U/05U Rev. A.3

F

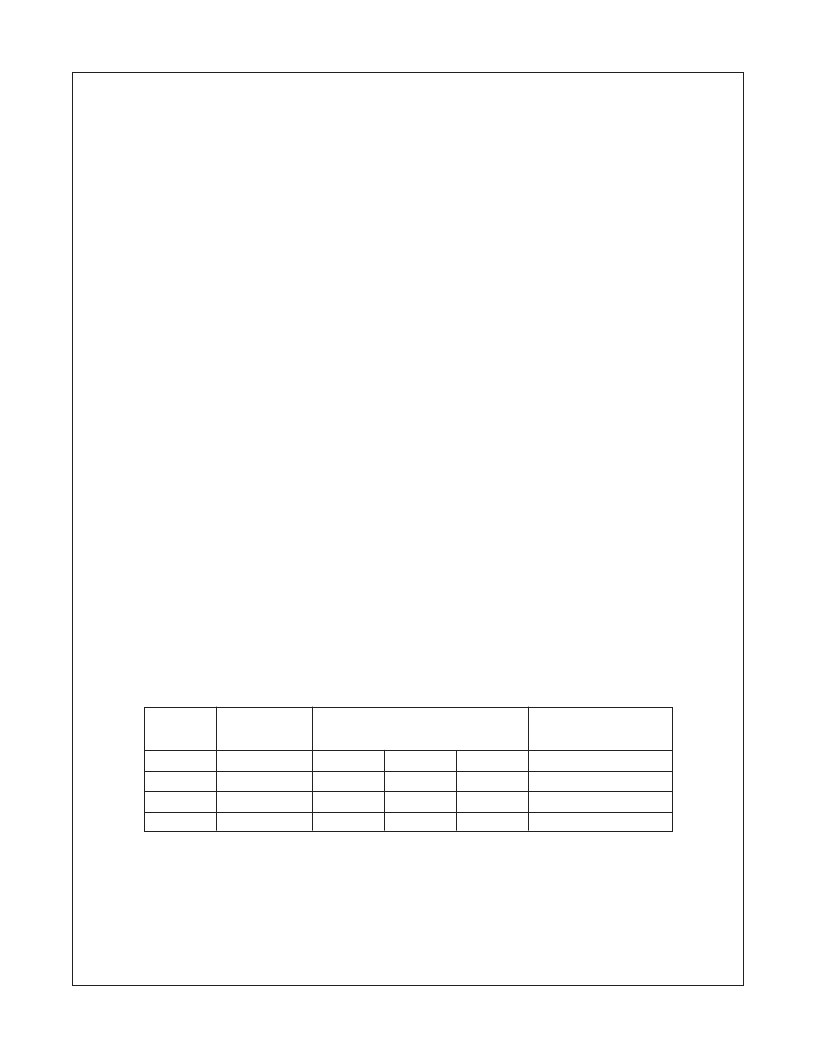

EEPROM

Density

Number of

Page Blocks

Device Selection Inputs

Provided

Address Bits

Selecting Page Block

2k bit

1

A0

A1

A2

None

4k bit

2

—

A1

A2

A0

8k bit

4

—

—

A2

A0 and A1

16k bit

8

—

—

—

A0, A1 and A2

Pin Descriptions

Serial Clock (SCL)

The SCL input is used to clock all data into and out of the device.

Serial Data (SDA)

SDA is a bi-directional pin used to transfer data into and out of the

device. It is an open drain output and may be wire

–

ORed with any

number of open drain or open collector outputs.

Write Protect (WP) (FM24C05U Only)

If tied to V

CC

, PROGRAM operations onto the upper half (upper

2Kbits) of the memory will not be executed. READ operations are

possible. If tied to V

SS

, normal operation is enabled, READ/

WRITE over the entire memory is possible.

This feature allows the user to assign the upper half of the memory

as ROM which can be protected against accidental programming.

When write is disabled, slave address and word address will be

acknowledged but data will not be acknowledged.

This pin has an internal pull-down circuit. However, on systems

where write protection is not required it is recommended that this

pin is tied to V

SS

.

Device Selection Inputs A2, A1 and A0 (as

appropriate)

These inputs collectively serve as

“

chip select

”

signal to an

EEPROM when multiple EEPROMs are present on the same IIC

bus. Hence these inputs, if present, should be connected to V

CC

or V

in a unique manner to allow proper selection of an EEPROM

amongst multiple EEPROMs. During a typical addressing se-

quence, every EEPROM on the IIC bus compares the configura-

tion of these inputs to the respective 3 bit

“

Device/Page block

selection

”

information (part of slave address) to determine a valid

selection. For e.g. if the 3 bit

“

Device/Page block selection

”

is 1-

0-1, then the EEPROM whose

“

Device Selection inputs

”

(A2, A1

and A0) are connected to V

CC

-V

SS

-V

CC

respectively, is selected.

Depending on the density, only appropriate numbers of

“

Device

Selection inputs

”

are provided on an EEPROM. For every

“

Device

selection input

”

that is not present on the device, the correspond-

ing bit in the

“

Device/Page block selection

”

field is used to select

a

“

Page Block

”

within the device instead of the device itself.

Following table illustrates the above:

Note that even when just one EEPROM present on the IIC bus,

these pins should be tied to V

CC

or V

SS

to ensure proper termina-

tion.

Device Operation

The FM24C04U/05U supports a bi-directional bus oriented proto-

col. The protocol defines any device that sends data onto the bus

as a transmitter and the receiving device as the receiver. The

device controlling the transfer is the master and the device that is

controlled is the slave. The master will always initiate data

transfers and provide the clock for both transmit and receive

operations. Therefore, the FM24C04U/05U will be considered a

slave in all applications.

Clock and Data Conventions

Data states on the SDA line can change only during SCL LOW.

SDA state changes during SCL HIGH are reserved for indicating

start and stop conditions. Refer to Figure 1 and Figure 2 on next

page.

Start Condition

All commands are preceded by the start condition, which is a

HIGH to LOW transition of SDA when SCL is HIGH. The

FM24C04U/05U continuously monitors the SDA and SCL lines for

the start condition and will not respond to any command until this

condition has been met.

Stop Condition

All communications are terminated by a stop condition, which is a

LOW to HIGH transition of SDA when SCL is HIGH. The stop

condition is also used by the FM24C04U/05U to place the device

in the standby power mode, except when a Write operation is

being executed, in which case a second stop condition is required

after t

WR

period, to place the device in standby mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM24C05UFLZVM8 | I2C Serial EEPROM |

| FM24C05UFLZVMT8 | I2C Serial EEPROM |

| FM24C05UFLZVN | I2C Serial EEPROM |

| FM24C05UFM8 | I2C Serial EEPROM |

| FM24C05UFMT8 | I2C Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM24C05UFLZVM8 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:I2C Serial EEPROM |

| FM24C05UFLZVMT8 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:I2C Serial EEPROM |

| FM24C05UFLZVN | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:I2C Serial EEPROM |

| FM24C05UFM8 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 SOIC-8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM24C05UFM8X | 功能描述:電可擦除可編程只讀存儲(chǔ)器 DISC BY MFG 7/03 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。