- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382968 > FS451 (Electronic Theatre Controls, Inc.) i-Net TV Interface Video Processor PDF資料下載

參數(shù)資料

| 型號(hào): | FS451 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | i-Net TV Interface Video Processor |

| 中文描述: | 一至網(wǎng)絡(luò)電視接口視頻處理器 |

| 文件頁(yè)數(shù): | 34/60頁(yè) |

| 文件大?。?/td> | 266K |

| 代理商: | FS451 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

FS450, FS451

PRELIMINARY PRODUCT DESCRIPTION

JUNE, 2000, VERSION 1.2

34

COPYRIGHT

ó

1999, 2000 FOCUS ENHANCEMENTS, INC.

PRELIMINARY INFORMATION

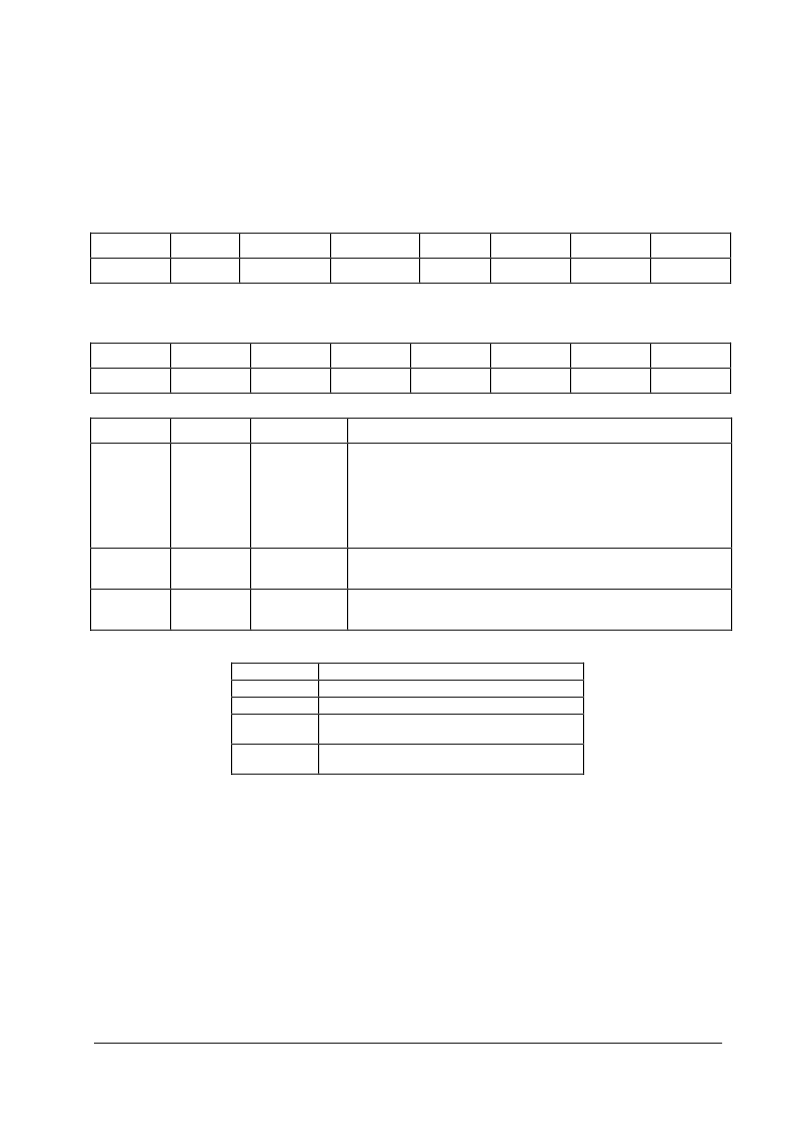

6.2.14 MISC - Miscellaneous Bits 34, 35 Register

Miscellaneous Bits Register (34)

7

6

5

4

3

2

1

0

0

0

NCO_LOAD

1

NCO_LOAD

0

0

0

0

0

Miscellaneous Bits Register (35)

7

6

5

4

3

2

1

0

GTLIO_PD

0

0

0

0

0

VGACKDIV

0

Reg

Bit#

Bit Name

Description

34

5,4

NCO_LOAD

1-0

NCO Load Control Bits.

The PLL M and N dividers and the

NCO Numerator (NCON) and denominator (NCOD) share the

same address (separate memory). The NCO Load Control bits

determine which registers are loaded when the NCON and

NCOD registers are written (see table below). M uses the lower

11 bits of NCON, and N uses the lower 11 bits of NCOD.

35

1

VGACKDIV

VGA Clock Divide.

Setting this bit divides the internal clock by

2 when the VGA input is in decimation (for XGA) mode.

35

7

GTLIO_PD

GTL I/O Power Down.

Setting this bit puts all the GTL pins

into power down mode.

Notes:

NCO_LOAD

0

1

2

Meaning

Load NCO Numerator and Denominator only.

Load M and N PLL Dividers only.

Load NCO Numerator and Denominator and

set M=512, N=128.

Load M and N PLL Dividers and set NCO

Numerator and Denominator both to 50.

3

Table 5: NCO_LOAD Control Bits

1) M is loaded with the desired value -2

2) N is loaded with the desired value -1

3) Using the 24 bit NCON and NCOD yields a very fine frequency resolution of 1.5 Hz but dithers the clock.

The speed of the clock dither is sufficiently limited by the narrowband (around 5 kHz) PLL to prevent any

problem with data transfers to the FS450. In fact, it provides an advantage for passing EMI certification

and behaves much like off the shelf dithered clocks designed specifically for that purpose.

4) Using the 11 bit M/N ratio gives a frequency resolution of 13 kHz, but it has no dithering. This is ideal for

dual VGA monitor and TV applications. Dithering the clock to a VGA controller makes the lines wiggle on

the connected VGA monitor, making it difficult to read. This however limits the scaling possibilities, and

close attention has to be paid to the factors of the VGA/TV pixels and lines so that they cancel down to 11

bit M and N numbers.

5) Both M/N and Numerator/Denominator can be used together, to generate a compromise performance.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FS451AC | i-Net TV Interface Video Processor |

| FS6011-02 | DIGITAL AUDIO/VIDEO CLOCK GENERATOR IC |

| FS6118 | CLOCK GENERATOR IC |

| FS6118-01 | CLOCK GENERATOR IC |

| FS612509-01 | 1:9 ZERO DELAY CLOCK BUFFER IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS451AC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:i-Net TV Interface Video Processor |

| FS4575-6-99 | 制造商:Schaffner 功能描述:IEC inline filtered cord set,6A 250Vac |

| FS4726-20-06-1 | 制造商:Schaffner 功能描述: |

| FS4744-20-07-2 | 制造商:Schaffner 功能描述: 制造商:SCHAFFNER EMC 功能描述: |

| FS48-023 | 功能描述:電源變壓器 48V CT 1.1VA XFMR DUAL PRIMARY 8 PIN RoHS:否 制造商:Triad Magnetics 功率額定值:12 VA 初級(jí)電壓額定值:115 V / 230 V 次級(jí)電壓額定值:12 V / 24 V 安裝風(fēng)格:SMD/SMT 一次繞組:Dual Primary Winding 二次繞組:Dual Secondary Winding 長(zhǎng)度:2.5 in 寬度:2 in 高度:1.062 in |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。