- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67595 > G2995F1UF (Global Mixed-mode Technology Inc.) DDR Termination Regulator PDF資料下載

參數(shù)資料

| 型號(hào): | G2995F1UF |

| 廠商: | Global Mixed-mode Technology Inc. |

| 英文描述: | DDR Termination Regulator |

| 中文描述: | DDR終端穩(wěn)壓器 |

| 文件頁(yè)數(shù): | 12/12頁(yè) |

| 文件大?。?/td> | 272K |

| 代理商: | G2995F1UF |

Ver: 1.7

May 10, 2005

TEL: 886-3-5788833

http://www.gmt.com.tw

9

G2995

Global Mixed-mode Technology Inc.

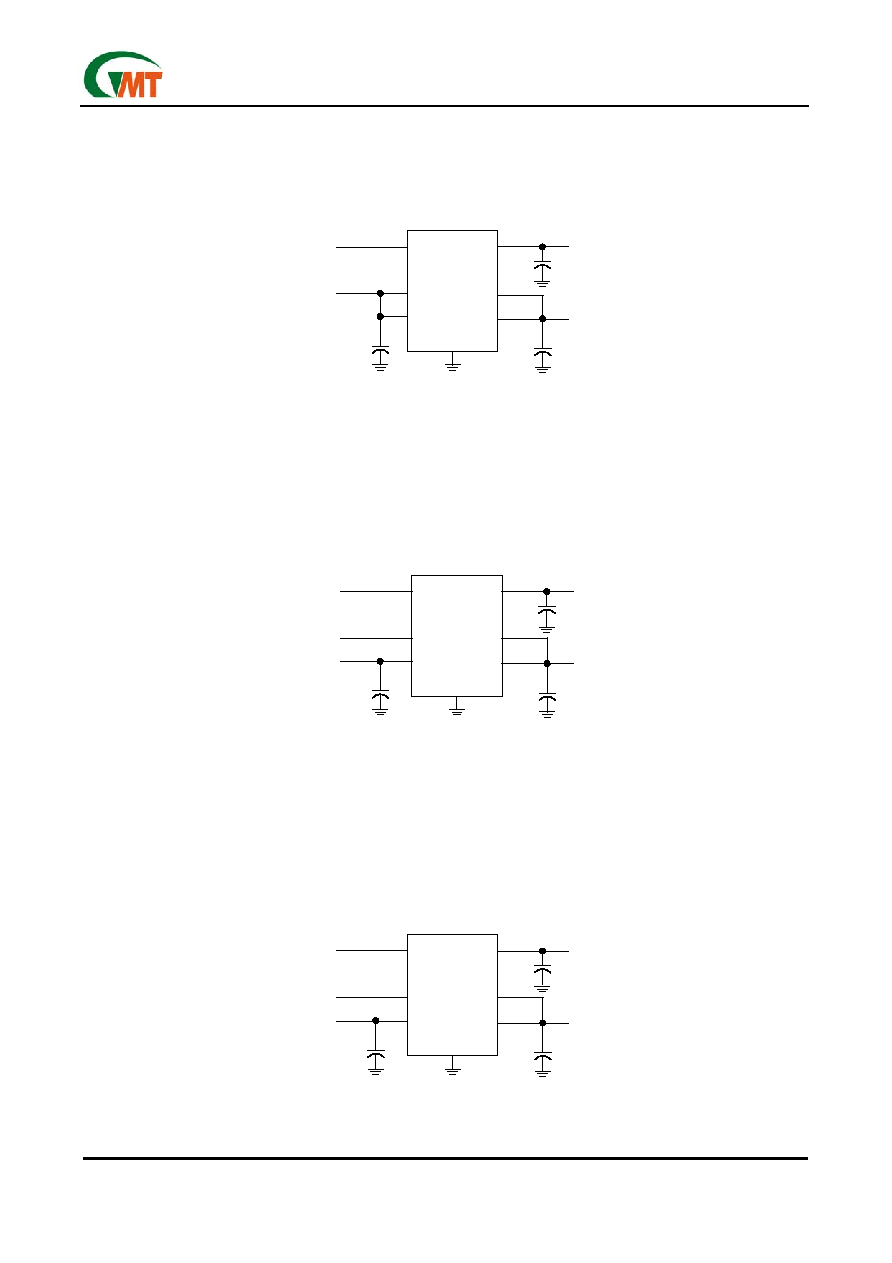

Typical Application Circuits

There are several application circuits shown in Figure

2 through 8 to illustrate some of the possible configu-

rations of the G2995. Figure 2~4 are the SSTL-2 ap-

plications. For the majority of applications that imple-

ment the SSTL-2 termination scheme, it is recom-

mended to connect all the input rails to 2.5V rail, as

seen in Figure 2. This provides an optimal trade-off

between power dissipation and component count.

In Figure 3, the power rails are split. The power rail of

the output stage (PVIN) can be as low as 1.8V, the

power rail of the analog circuit (AVIN) is operated

above 2V. The lower output stage power rail can lower

the internal power dissipation when sourcing from the

device and improve the efficiency, but the disadvan-

tage is the maximum continuous current sourcing from

VTT is reduced. This configuration is applied when the

power dissipation and efficiency are concerned.

In Figure 4, the power rail of the output stage (PVIN) is

connected to 3.3V to increase the maximum continu-

ous current sourcing from VTT. AVIN should be always

equal to or larger than PVIN. This configuration can

increase the source capability of this device, but the

power dissipation increases at the same time. It

should be more careful to prevent the junction tem-

perature from exceeding the maximum rating. Be-

cause of this risk, it is not recommended to supply the

output stage power rail (PVIN) with a voltage higher

than a nominal 3.3V rail.

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

V

DD=2.5V

C

IN

Figure 2. Recommended SSTL-2 Implementation

C

OUT

C

REF

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

V

DD=2.5V

C

IN

Figure 2. Recommended SSTL-2 Implementation

C

OUT

C

REF

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

AV

IN=3.3V or 5V

C

IN

Figure 4. SSTL-2 Implementation with higher voltage rails

C

OUT

C

REF

PV

IN=3.3V

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

AV

IN=3.3V or 5V

C

IN

Figure 4. SSTL-2 Implementation with higher voltage rails

C

OUT

C

REF

PV

IN=3.3V

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

AV

IN=1.8V or 5.5V

C

IN

Figure 3. Lower Power Dissipation SSTL-2 Implementation

C

OUT

C

REF

PV

IN=1.8V

+

V

REF

V

DDQ

AV

IN

V

SENSE

PV

IN

V

TT

GND

V

TT=1.25V

V

REF=1.25V

V

DDQ=2.5V

AV

IN=1.8V or 5.5V

C

IN

Figure 3. Lower Power Dissipation SSTL-2 Implementation

C

OUT

C

REF

PV

IN=1.8V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| G2995P1U | DDR Termination Regulator |

| G2995P1UF | DDR Termination Regulator |

| G2996F1UF | DDR I/II Termination Regulator |

| G2996F1U | DDR I/II Termination Regulator |

| G2996P1UF | DDR I/II Termination Regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| G2995P1U | 制造商:GMT 制造商全稱:Global Mixed-mode Technology Inc 功能描述:DDR Termination Regulator |

| G2995P1UF | 制造商:GMT 制造商全稱:Global Mixed-mode Technology Inc 功能描述:DDR Termination Regulator |

| G2996 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DDR Termination Regulator with STR function.|Terminator Series |

| G2996F1U | 制造商:GMT 制造商全稱:Global Mixed-mode Technology Inc 功能描述:DDR I/II Termination Regulator |

| G2996F1UF | 制造商:GMT 制造商全稱:Global Mixed-mode Technology Inc 功能描述:DDR I/II Termination Regulator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。