- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375996 > GD16132-GLP ATM Multiplexer PDF資料下載

參數(shù)資料

| 型號(hào): | GD16132-GLP |

| 英文描述: | ATM Multiplexer |

| 中文描述: | ATM多路復(fù)用器 |

| 文件頁(yè)數(shù): | 1/11頁(yè) |

| 文件大?。?/td> | 114K |

| 代理商: | GD16132-GLP |

General Description

The GD16131, 32:4 / Quad 8:1 MUX and

the GD16132, 4:32 / Quad 1:8 DeMUX

are intended for use in 2.5 Gbit/s trans-

mission systems. The high-speed inter-

face is designed to accommodate the

requirements of the GD16554 (4:1 MUX)

and the GD16543 (1:4 DeMUX) both

meeting CCITT specifications at

2.5 Gbit/s SDH STM-16. The GD16131

and GD16162 take care of the interface

between the high-speed devices differen-

tial ECL level I/O’s at 622 Mbit/s and

lower speed CMOS gate arrays at

78 Mbit/s. Hence they are dual supply

devices shifting levels between true ECL

and TTL.

The GD16131 and GD16132 are made

as four identical blocks of 8 bit and a

clock driver circuit. The 8 bit blocks are

implemented as shift registers to obtain

the best speed/power ratio of the process

technology used. Also this means easy

clock distribution with small delay be-

tween incoming and outgoing signals.

For the GD16131 the 622 Mbit/s data

outputs are re-timed at the chip edge to

cut down delay from clock-in to data-out,

allowing counter directional clocking.

Thus the on-chip delay, except output

buffer load dependant delay, is kept be-

low 1 ns. A 622 MHz output clock with

close timing relation to the data outputs

also allows co-directional clocking. On

both MUX and DeMUX, the subdivided

78 MHz clock are also re-timed at the

chip edge to cut down delay from the

622 MHz input clock. The phase relation

between low-speed data and the subdi-

vided output clock are selectable in four

phases.

The GD16131 and GD16132 are pack-

aged in 68 pin Multi Layer Ceramic

(MLC) packages, yielding excellent high-

speed signal accommodation and ther-

mal conditions. The chip set is designed

for an operating temperature between

–5

°

C and +85

°

C, case temperature.

With power consumption of 1.3 W typical

for both GD16131 and GD16132, only

little or no heat sink is required.

Bit naming convention

Naming of pins on parallel ports is made

assuming the transfer bit order to be in-

creasing starting with position D0, D1, ...,

D31.

Features

GD16131

l

Quad 8:1 MUX

l

All high-speed I/O’s are differential,

ECL level.

l

All low-speed I/O’s are TTL level,

outputs drive 10 pF at 78 MHz.

l

Subdivided output clock to data rela-

tion selectable in four phases.

l

Dual supply: +5 V, -5.2 V.

l

68 pin MLC flat package.

l

High-speed pins on single side of

package for easy PCB routing.

l

Power consumption: 1.3 W typical.

GD16132

l

Quad 1:8 DeMUX

l

All high-speed I/O’s are differential,

ECL level.

l

All low-speed I/O’s are TTL level,

outputs drive 10 pF at 78 MHz.

l

Subdivided output clock to data

relation selectable in four phases.

l

Dual supply: +5 V, -5.2 V.

l

68 pin MLC flat package.

l

High-speed pins on single side of

package for easy PCB routing.

l

Power consumption: 1.3 W typical.

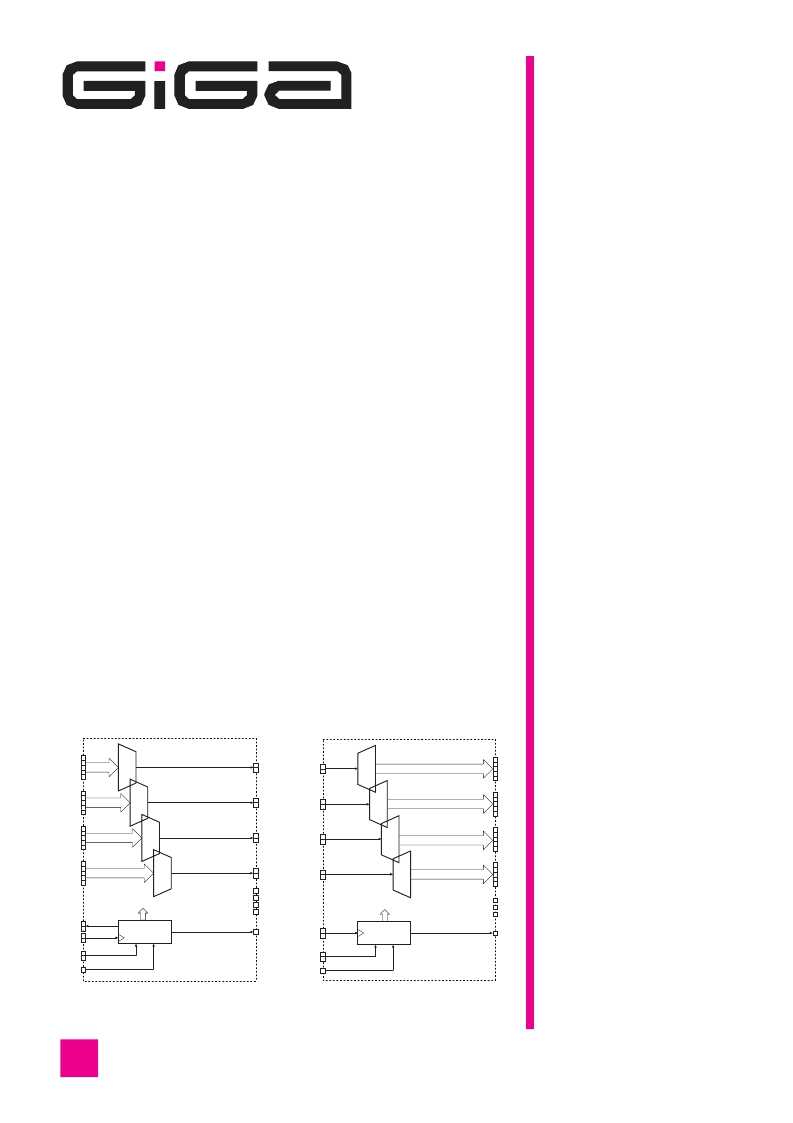

622 Mbit/s

MUX/DeMUX

Chip Set

GD16131/GD16132

D

D0

D4

:

D24

D28

D1

D5

:

D25

D29

D2

D6

:

D26

D30

D3

D7

:

D27

D31

CKOP

CKON

Clock

Generator

CKIP

CKIN

SEL1

SEL2

CKOUT

VCC

VDD

VEE

VTT

DO3P

DO3N

DO2P

DO2N

DO1P

DO1N

DO0P

DO0N

RESET

SEL1

SEL2

RESET

Clock

Generator

CKIP

CKIN

CKOUT

VCC

VDD

VEE

D0

D4

:

D24

D28

D1

D5

:

D25

D29

D2

D6

:

D26

D30

D3

D7

:

D27

D31

DI0P

DI0N

DI1P

DI1N

DI2P

DI2N

DI3P

DI3N

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GD4001BC | Quad 2-input NOR Gate |

| GD4001BDC | Quad 2-input NOR Gate |

| GD4002BC | Dual 4-input NOR Gate |

| GD4011BC | Quad 2-input NAND Gate |

| GD4011BDC | Quad 2-input NAND Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GD1626 | 制造商:Burndy 功能描述:GROUND CONNECTOR |

| GD1629 | 制造商:Burndy 功能描述:GROUND CONNECTOR |

| GD16333-QFP100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Demultiplexer |

| GD16367B-52BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM Multiplexer |

| GD16368B-52BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Demultiplexer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。