- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375998 > GL841 GL841 USB 2.0 2-in-1 Scanner Controller PDF資料下載

參數(shù)資料

| 型號(hào): | GL841 |

| 英文描述: | GL841 USB 2.0 2-in-1 Scanner Controller |

| 中文描述: | GL841的USB 2.0 2合1掃描儀控制器 |

| 文件頁(yè)數(shù): | 10/50頁(yè) |

| 文件大小: | 1688K |

| 代理商: | GL841 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)

GL841 USB 2.0 2-in-1 Scanner Controller

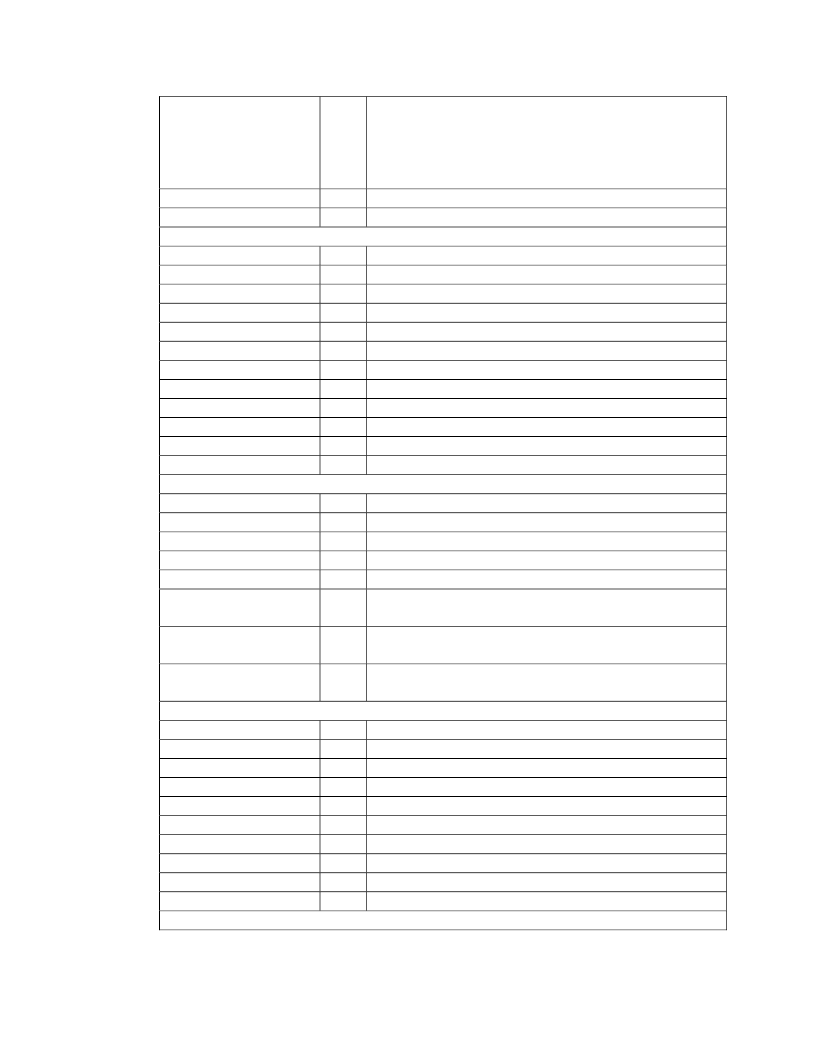

MT_PH0=I02

Uni-polar(2003) : MT_PH3=PHASE A

MT_PH2=PHASE B

MT_PH1=PHASE /A

MT_PH0=PHASE /B

MOTORTGO(GPIO13)

O

Output motor trigger for ADF scanning or GPIO13.

HOME

I

Sense carriage home position

CCD/CIS Control Signals

CCD_CK1X

O

CCD Shift register clock1 or CIS clock output

CCD_CK2X

O

CCD Shift register clock2 or CIS clock output

CCD_CPX

O

CCD Clamp gate clock or CIS clock output

CCD_RSX

O

CCD Reset gate clock or CIS clock output

CCD_TGX

O

CCD Transfer gate clock for R channel or CIS Line start pulse

CCD_TGG

O

CCD Transfer gate clock for G channel

CCD_TGB

O

CCD Transfer gate clock for B channel

CCD_CK3X

O

CCD Shift register clock3

CCD_CK4X

O

CCD Shift register clock4

LAMP_SW

O

Flatbed lamp power control or CIS Red LED array control

XPA_SW

O

Transparency lamp power control or CIS Green LED array control

LED_B

O

CIS Blue LED array control

FRONT-END

OP0~7

I

AFE digital data input.

SEN/SLOAD

O

Serial interface load pulse.

SCLK

O

Serial interface clock output.

SDI

O

Serial data output.

SDO

I

Serial data input.

BSMP/CDSCLK1

O

Wolfson type : Video sample synchronization pulse.

Analog Device : CDS Reference level sampling clock.

VSMP/CDSCLK2

O

Wolfson type : Video sample synchronization pulse.

Analog Device : CDS Data level sampling clock.

MCLK/ADCCLK

O

Wolfson type : Master clock.

Analog Device : A/D Converter sampling clock.

DRAM

DBUS0~15

B

DRAM data bus

ABUS0~9

O

DRAM address bus

RASX

O

DRAM RAS signal of first memory chip

CASX

O

DRAM CAS signal of first memory chip

NOEX

O

DRAM OE(output enable) signal of first memory chip

NWEX

O

DRAM WE signal of first memory chip

RASY

O

DRAM RAS signal of second memory chip

CASY

O

DRAM CAS signal of second memory chip

NOEY

O

DRAM OE(output enable) signal of second memory chip

NWEY

O

DRAM WE signal of second memory chip

Miscellaneous

Version 1.7

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GL8EG31 | Optoelectronic |

| GL8HD31 | Optoelectronic |

| GL8HS31 | Optoelectronic |

| GL8KG31 | Optoelectronic |

| GL8HY41 | Optoelectronic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GL842 | 制造商:GENESYS 制造商全稱:GENESYS 功能描述:USB 2.0 2-in-1 Scanner Controller |

| GL843 | 制造商:GENESYS 制造商全稱:GENESYS 功能描述:High Speed USB 2.0 With ADF 2-in-1 Scanner Controller |

| GL848 | 制造商:GENESYS 制造商全稱:GENESYS 功能描述:High Speed USB 2.0 |

| GL850 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:USB 2.0 4-PORT HUB Controller |

| GL850A | 制造商:GENESYS 制造商全稱:GENESYS 功能描述:USB 2.0 Low-Power HUB Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。