- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67672 > GP1R (Mitel Networks Corporation) Dual Mode CDMA/AMPS Baseband Interface PDF資料下載

參數(shù)資料

| 型號(hào): | GP1R |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Dual Mode CDMA/AMPS Baseband Interface |

| 中文描述: | 雙模式CDMA / AMPS二元基帶接口 |

| 文件頁(yè)數(shù): | 11/15頁(yè) |

| 文件大?。?/td> | 139K |

| 代理商: | GP1R |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

5

PLUTO

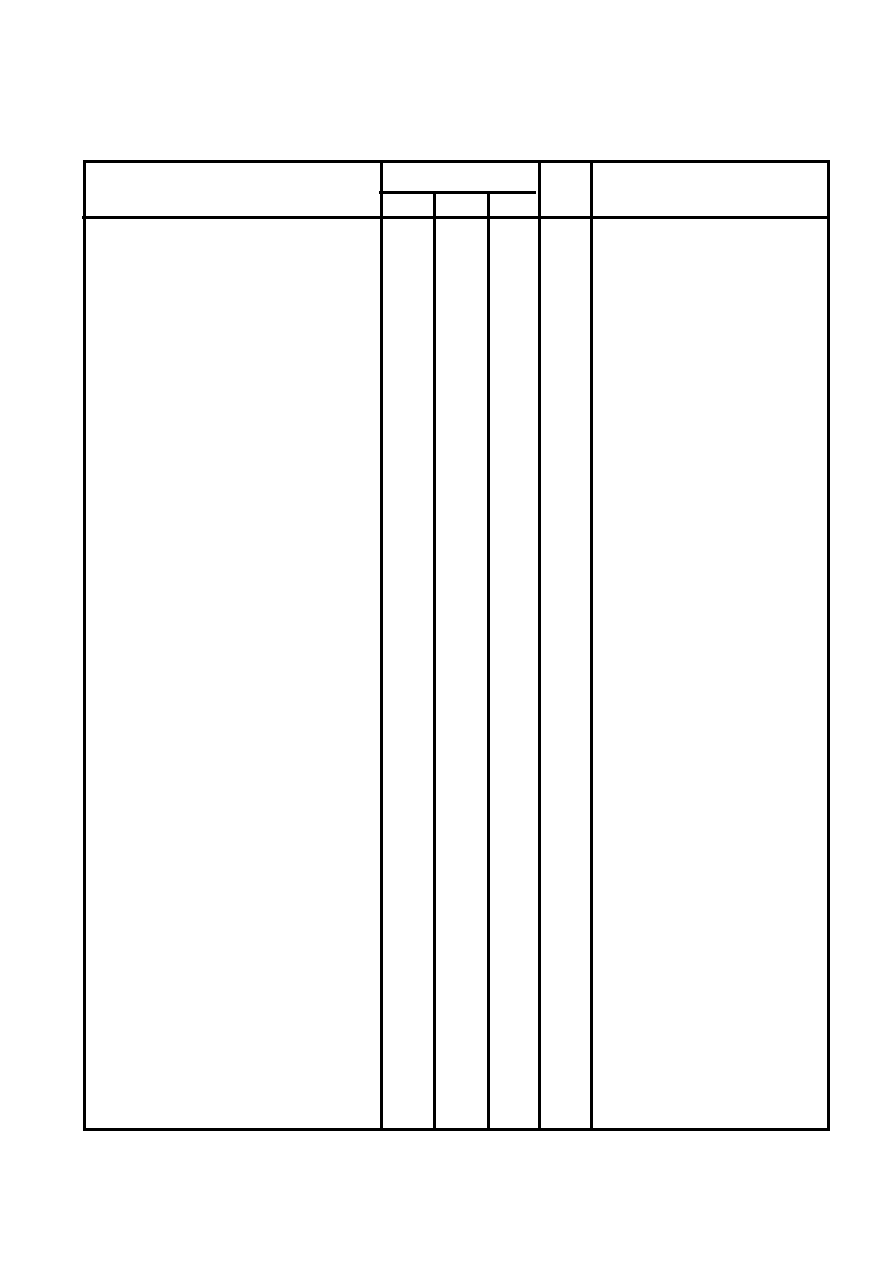

Parameter

Value

Units

Conditions

Min

Typ

Max

t1

TXCLOCK PERIOD (CDMA TX)

203.2

ns

CDMA TX Figure 3

t2

TXCLOCK HIGH TIME (CDMA TX)

101.6

ns

CDMA TX Figure 3

t3

TXCLOCK LOW TIME (CDMA TX)

101.6

ns

CDMA TX Figure 3

t4

TXCLOCK PHASE Delay (CDMA TX)

1.2

ns

CDMA TX Figure 3, FM TX Figure 4

t5

TXCLOCK RISE TIME (CDMA TX)

12

ns

CDMA TX Figure 3, FM TX Figure 4

t6

TXCLOCK FALL TIME (CDMA TX)

12

ns

CDMA TX Figure 3, FM TX Figure 4

t7

TXD-TXCLOCK SETUP TIME

20

ns

CDMA TX Figure 3, FM TX Figure 4

t8

TXCLOCK-TXD HOLD TIME

3

ns

CDMA TX Figure 3, FM TX Figure 4

t11

TXCLOCK PERIOD (FM TX)

2.78

s

FM TX Figure 4

t12

TXCLOCK HIGH TIME (FM TX)

1.39

s

FM TX Figure 4

t13

TXCLOCK LOW TIME (FM TX)

1.39

s

FM TX Figure 4

t14

CHIPx8 PERIOD

101.6

ns

Figure 5

t15

CHIPx8 HIGH TIME

50.8

ns

Figure 5

t16

CHIPx8LOW TIME

50.8

152.4

ns

Figure 5

t17

CHIPx8 RISE TIME

3

12

ns

Figure 5

t18

CHIPx8 FALL TIME

3

12

ns

Figure 5

t19

RXD Hold Time After CHIPx8

↓

10

ns

Figure 5

t20

RXD DELAY After CHIPx8

↓

20

ns

Figure 5

t21

FMCLK PERIOD

2.78

s

FM RX Figure 6

t22

FMCLK HIGH TIME

1.39

s

FM RX Figure 6

t23

FMCLK LOW TIME

1.39

s

FM RX Figure 6

t24

FMCLK RISE TIME

12

ns

FM RX Figure 6

t25

FMCLK FALL TIME

12

ns

FM RX Figure 6

t26

RXFMSTB HIGH TIME

1

s

FM RX Figure 6

t27

RXFMSTB -FMCLK

↓ SETUP TIME

50

ns

FM RX Figure 6

t28

FMCLK

↓ RXFMSTB HOLD TIME

50

ns

FM RX Figure 6

t29

FMCLK

↓ OUTPUT DATA DELAY

50

ns

FM RX Figure 6

t30

ADCENA HIGH _ CONVERSION

40

s

General purpose ADC Figure 7

t31

ADCENA HIGH TIME

100

ns

General purpose ADC Figure 7

t32

ADCENA LOW TIME

100

ns

General purpose ADC Figure 7

t33

ADCCLK PERIOD

2.44

s

General purpose ADC Figure 7

t34

ADCCLK HIGH TIME

0.81

s

General purpose ADC Figure 7

t35

ADCCLK LOW TIME

1.62

s

General purpose ADC Figure 7

t36

ADCCLK RISE TIME

12

ns

General purpose ADC Figure 7

t37

ADCCLK FALL TIME

12

ns

General purpose ADC Figure 7

t38

ADCDATA VALID BEFORE ADCCLK

↑

1

s

General purpose ADC Figure 7

t39

ADC DATA HOLD TIME

5

ns

General purpose ADC Figure 7

t40

SCLK-SDATA setup time

20

ns

Serial Interface Figure 8

t41

SCLK-SDATA hold time

20

ns

Serial Interface Figure 8

t42

SCLK pulse width

50

ns

Serial Interface Figure 8

t43

SLATCH-SCLK setup time

20

ns

Serial Interfsce Figure 8

t44

SLATCH pulse width

50

ns

Serial Interface Figure 8

t45

SCLK period

100

ns

Serial Interface Figure 8

TIMING INFORMATION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GP2000 | () |

| GP2010 | GPS Receiver RF Front End |

| GP2010 | GPS Receiver RF Front End(用于全球定位系統(tǒng)(GPS)接收器的第二代RF前端) |

| GP2015 | Aluminum Electrolytic Radial Leaded Low Profile Wide Temp Capacitor; Capacitance: 22uF; Voltage: 25V; Case Size: 5x9 mm; Packaging: Bulk |

| GP2015 | GPS Receiver RF Front End(用于全球定位系統(tǒng)(GPS)接收器的第二代RF前端) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GP1R11D5000 | 制造商:Coto Technology 功能描述: |

| GP1R21A0000 | 制造商:SRC Devices 功能描述: |

| GP1R21AD000 | 制造商:SRC Devices 功能描述: |

| GP1S01 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:HIGH SPEED PHOTOINTERRUPTER |

| GP1S01F | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:HIGH SPEED PHOTOINTERRUPTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。