- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383014 > GS1522 (Electronic Theatre Controls, Inc.) HDTV Serial Digital Serializer PDF資料下載

參數(shù)資料

| 型號: | GS1522 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | HDTV Serial Digital Serializer |

| 中文描述: | 高清晰度電視串行數(shù)字串行 |

| 文件頁數(shù): | 11/20頁 |

| 文件大?。?/td> | 414K |

| 代理商: | GS1522 |

GENNUM CORPORATION

522 - 26 - 00

11

G

During pathological signals, the amount of jitter that the

phase detector will add can be calculated. By choosing the

proper loop bandwidth, the amount of phase detector

induced jitter can also be limited. Typically, for a 1.41MHz

loop bandwidth at 0.2UI input jitter modulation, the phase

detector induced jitter is about 0.015UIp-p. This is not very

significant, even for the pathological signals.

9. CHARGE PUMP

The charge pump in a slew PLL is different from the charge

pump in a linear PLL. There are two main functions of the

charge pump. One function is to hold the frequency

information of the input data. This information is held by

C

CP1

, which is connected between LFS (82) and LFS (84).

The other capacitor, C

CP2

between LFS and LFA_V

EE

(89) is

used to remove common mode noise. Both C

CP1

and C

CP2

should have the same value. The second function of the

charge pump is to provide a binary control voltage to the

VCO depending upon the phase detector output. The

output pin, LFA (90) controls the VCO. Internally there is a

500

pull-up resistor, which is driven with a 100μA current

called

Ι

P

. Another analog current

Ι

F

, with 5mA maximum

drive proportional to the voltage across the C

CP1

is applied

at the same node. The voltage at the LFA node is

V

LFA_VCC

- 500(

Ι

P

+

Ι

F

) at any time.

Because of the integrator,

Ι

F

changes very slowly, whereas

Ι

P

could change at the positive edge of the data transition

as often as a clock period. In the locked position, the

average voltage at LFA (V

LFA_VCC

–

500(

Ι

P

/2+

Ι

F

) is such that

VCO generates frequency

, equal to the data rate clock

frequency. Since

Ι

P

is changing all the time between 0A and

100μA, there will be two levels generated at the LFA output.

10. VCO

The GO1515 is an external hybrid VCO, which has a centre

frequency of 1.485GHz and is also guaranteed to provide

1.485/1.001GHz within the control voltage (3.1V

–

4.65V) of

the GS1522 over process, power supply and temperature.

The GO1515 is a very clean frequency source and,

because of the internal high Q resonator, it is an order of

magnitude more immune to external noise as compared to

on-chip VCOs.

The VCO gain, K

, is nominally 16MHz/V. The control

voltage around the average LFA voltage will be 500 x

Ι

P

/2.

This will produce two frequencies off from the centre by

=K

x 500 x

Ι

P

/2.

11. LBCONT

The LBCONT pin (91) is used to adjust the loop bandwidth

by externally changing the internal charge pump current.

For maximum loop bandwidth, connect LBCONT to the

most positive power supply. For medium loop bandwidth,

connect LBCONT through a pull-up resistor (R

PULL-UP

). For

low loop bandwidth, leave LBCONT floating. The formula

below shows the change in the loop bandwidth using

R

PULL-UP.

where LBW

NOMINAL

is the loop bandwidth when LBCONT is

left floating.

12. LOOP BANDWIDTH OPTIMIZATION

Since the feed back loop has only digital circuits, the small

signal analysis does not apply to the system. The effective

loop bandwidth scales with the amount of input jitter

modulation index. The following table summarizes the

relationship between input jitter modulation index and

bandwidth when R

CP1

and C

CP3

are not used. See the

Typical Application Circuit artwork for the location of R

CP1

and C

CP3

.

The product of the input jitter modulation (IJM) and the

bandwidth (BW) is a constant. In this case, it is 282.9kHzUI.

The loop bandwidth automatically reduces with increasing

input jitter, which helps in cleaning up the signal as much

as possible.

Using a series combination of R

CP1

and C

CP3

in parallel to

an on-chip resistor (as shown in the Typical Application

Circuit) can reduce the loop bandwidth of the GS1522. The

parallel combination of the resistor is directly proportional to

the bandwidth factor. For example, the on-chip 500

resistor yields 282.9kHzUI. If a 50

resistor is connected in

parallel, the effective resistance will be (50:500) 45.45

.

This

resistance

yields

[282.9 x (45.45/500)] = 25.72kHzUI. The capacitance C

CP3

in series with the R

CP1

should be chosen such that the RC

factor is 50μF. For example, R

CP1

=50

would require

C

CP3

=1μF.

a

bandwidth

factor

of

The synchronous lock time increases with reduced

bandwidth. Nominal synchronous lock time is equal to

[

/Bandwidth

factor].

bandwidth factor (282.9kHzUI) would yield 1.25μs. For

That

is,

the

default

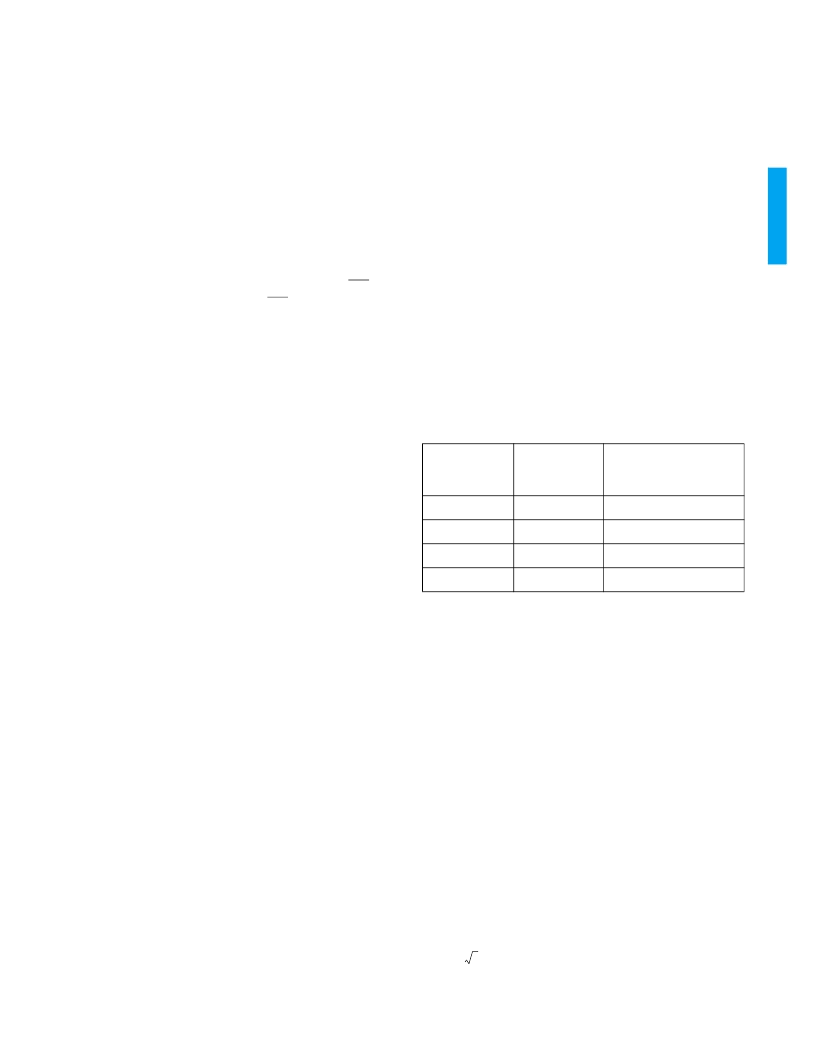

TABLE 1: Relationship Between Input Jitter Modulation Index and

Bandwidth

INPUT JITTER

MODULATION

INDEX

BANDWIDTH

BW JITTER FACTOR

(jitter modulation x BW)

0.05

5.657MHz

282.9kHzUI

0.10

2.828MHz

282.9kHzUI

0.20

1.414MHz

282.9kHzUI

0.50

565.7kHz

282.9kHzUI

LBW

LBW

NOMINAL

25k

5k

(

R

PULL

+

-----------------+

)

UP

–

)

×

=

0.25

2

×

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS1522-CQR | HDTV Serial Digital Serializer |

| GS1540 | HDTV Serial Digital Non-Equalizing Receiver |

| GS1540-CQR | HDTV Serial Digital Non-Equalizing Receiver |

| GS1545 | HDTV Serial Digital Equalizing Receiver |

| GS1545-CQR | HDTV Serial Digital Equalizing Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS1522_04 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:HDTV Serial Digital Serializer |

| GS1522-CQR | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS1522-CQRE3 | 制造商:Gennum Corporation 功能描述:Monolithic Bipolar Integrated Circuit 128-Pin MQFP |

| GS1524 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:GS1524 HD-LINX-TM II Multi-Rate SDI Adaptive Cable Equalizer |

| GS1524_11 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:Multi-Rate SDI Adaptive Cable Equalizer |

發(fā)布緊急采購,3分鐘左右您將得到回復。