- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383014 > GS1545 (Electronic Theatre Controls, Inc.) HDTV Serial Digital Equalizing Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | GS1545 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | HDTV Serial Digital Equalizing Receiver |

| 中文描述: | 串行數(shù)字高清晰度電視接收機(jī)均等 |

| 文件頁數(shù): | 13/19頁 |

| 文件大?。?/td> | 198K |

| 代理商: | GS1545 |

GENNUM CORPORATION

522 - 28 - 00

13

G

DETAILED DESCRIPTION

The GS1545 is a single standard equalizing receiver for

serial

digital

HDTV

signals

1.485/1.001Gb/s.

at

1.485Gb/s

and

UNIQUE SLEW PHASE LOCK LOOP (S-PLL):

A unique feature of the GS1545 is the innovative slew phase

lock loop (S-PLL). When a step phase change is applied to

the PLL, the output phase gains constant rate of change

with respect to time. This behaviour is termed slew.

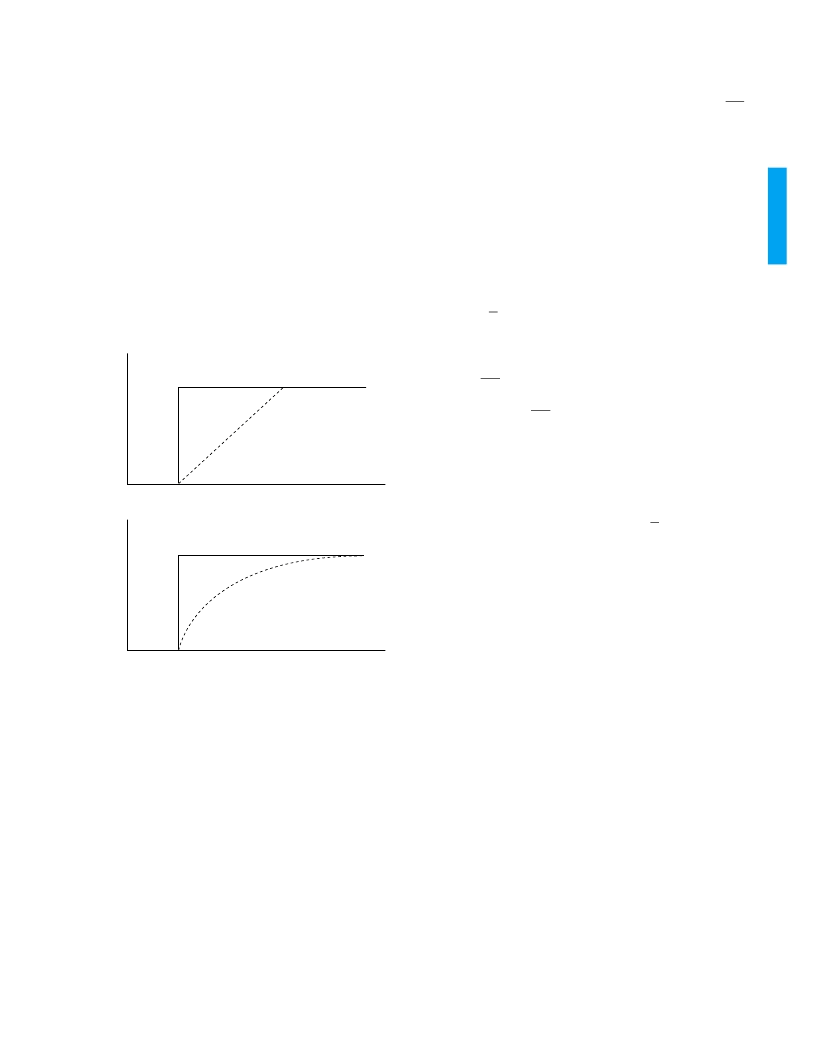

Figure 21 shows an example of input and output phase

variation over time for slew and linear (conventional) PLLs.

Since the slewing is a nonlinear behavior, the small signal

analysis cannot be done in the same way as the standard

PLL. However, it is still possible to plot input jitter transfer

characteristics at a constant input jitter modulation.

Fig. 21 PLL Characteristics

Slew PLLs offer several advantages such as excellent noise

immunity. Because of the infinite bandwidth for an infinitely

small input jitter modulation (or jitter introduced by VCO),

the loop corrects for that immediately thus the small signal

noise of the VCO is cancelled. The GS1545 uses a very

clean, external VCO called the GO1515 (refer to the

GO1515 Data Sheet for details). In addition, the bi-level

digital phase detector provides constant loop bandwidth

that is predominantly independent of the data transition

density. The loop bandwidth of a conventional tri-stable

charge pump drops with reducing data transitions. During

pathological signals, the data transition density reduces

from 0.5 to 0.05, but the slew PLL

’

s performance essentially

remains unchanged.

Because most of the PLL circuitry is digital, it is more like

other digital systems which are generally more robust than

their analog counterparts. Additionally, signals like DM/DM

which represent the internal functionality can be generated

without adding additional artifacts. Thus, system debugging

is also possible with these features. The complete slew PLL

is made up of several blocks including the phase detector,

the charge pump and an external Voltage Controlled

Oscillator (VCO).

DIGITAL INPUT BUFFER

The input buffer is a self-biased circuit. On-chip 50

termination resistors provide a seamless interface for other

HD-LINX

products such as the GS1504 Adaptive Cable

Equalizer. The digital input is selected by applying a logic

low to the A/D pin.

ANALOG INPUT

The HD serial data signal may be connected to the input

pins (SDI/SDI) in either a differential or single ended

configuration. AC coupling of the inputs is recommended,

as the SDI and SDI inputs are internally biased at

approximately 2.7 volts. The input signal passes through a

variable gain equalizing stage whose frequency response

closely matches the inverse cable loss characteristic. In

addition, the variation of the frequency response with

control voltage imitates the variation of the inverse cable

loss characteristic with cable length. The analog input is

selected by applying a logic high to the A/D pin.

The edge energy of the equalized signal is monitored by a

detector circuit which produces an error signal cor-

responding to the difference between the desired edge

energy and the actual edge energy. This error signal is

integrated by an internal AGC filter capacitor providing a

steady control voltage for the gain stage. As the frequency

response of the gain stage is automatically varied by the

application of negative feedback, the edge energy of the

equalized signal is kept at a constant level which is

representative of the original edge energy at the transmitter.

The equalized signal is also DC restored, effectively

restoring the logic threshold of the equalized signal to its

correct level independent of shifts due to AC coupling.

PHASE DETECTOR

The phase detector portion of the slew PLL used in the

GS1545 is a bi-level digital phase detector. It indicates

whether the data transition occurred before or after with

respect to the falling edge of the internal clock. When the

phase detector is locked, the data transition edges are

aligned to the falling edge of the clock. The input data is

then sampled by the rising edge of the clock, as shown in

Figure 22. In this manner, the allowed input jitter is 1UI p-p

in an ideal situation. However, due to setup and hold time,

the GS1545 typically achieves 0.5UI p-p input jitter

tolerance without causing any errors in this block. When the

0.2

0.1

0.0

INPUT

OUTPUT

SLEW PLL RESPONSE

P

0.2

0.1

0.0

INPUT

OUTPUT

LINEAR (CONVENTIONAL) PLL RESPONSE

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS1545-CQR | HDTV Serial Digital Equalizing Receiver |

| GS1881-IKA | Monolithic Video Sync Separators |

| GS1881-ITA | Monolithic Video Sync Separators |

| GS4881 | Monolithic Video Sync Separators |

| GS4881-CDA | Monolithic Video Sync Separators |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS1545_04 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:HDTV Serial Digital Equalizing Receiver |

| GS1545-CQR | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS1545-CQRE3 | 制造商:Semtech Corporation 功能描述:High Performance integrated Equalizing Receiver 128-Pin MQFP 制造商:Semtech Corporation 功能描述:HD Equalizing Receiver |

| GS1550MD-EVK2-S2W-WEB | 制造商:GSC 功能描述:GS1550MD Evaluation Kit Includes the GS1550MD-EVB2-S2W-WEB Evaluation Board |

| GS1559 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:GS1559 HD-LINX-TM II Multi-Rate Deserializer with Loop-Through Cable Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。