- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370404 > GVT73128A8SJ-12L x8 SRAM PDF資料下載

參數(shù)資料

| 型號: | GVT73128A8SJ-12L |

| 英文描述: | x8 SRAM |

| 中文描述: | x8的SRAM |

| 文件頁數(shù): | 6/11頁 |

| 文件大小: | 87K |

| 代理商: | GVT73128A8SJ-12L |

AC TEST CONDITIONS

Input pulse levels

0V to 3.0V

Input rise and fall times

1.5ns

Input timing reference levels

1.5V

Output reference levels

1.5V

Output load

See Figures 1 and 2

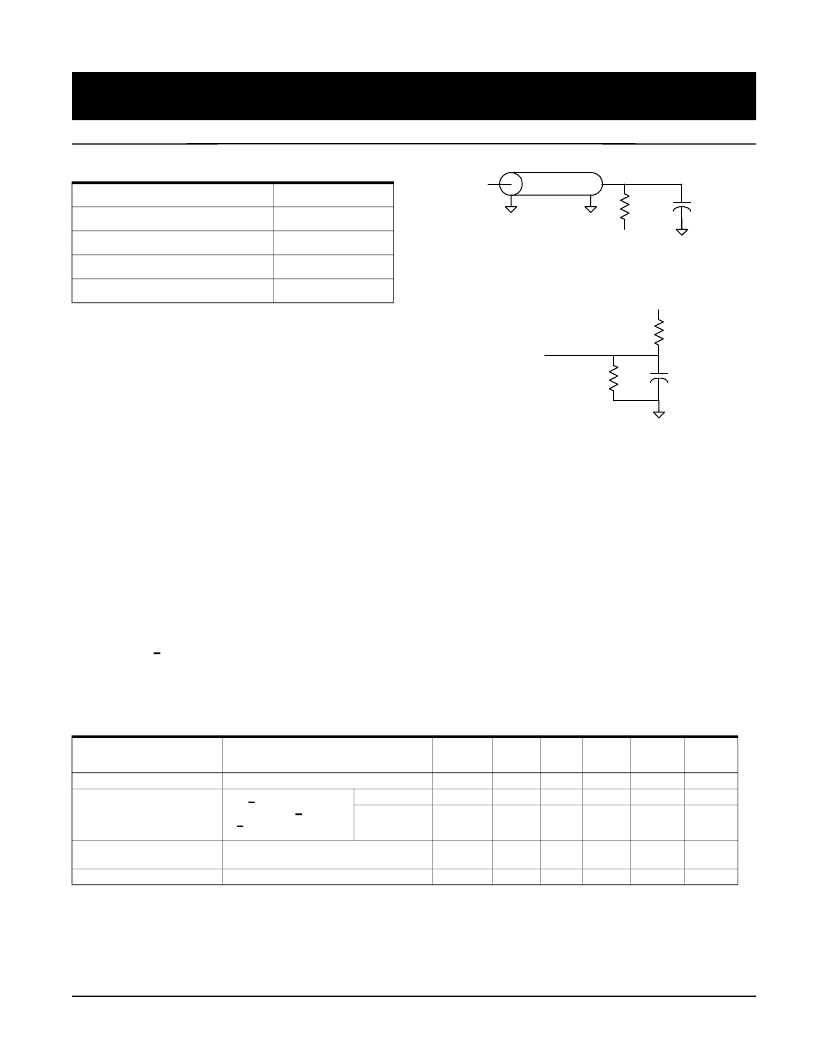

OUTPUT LOADS

Vt = 1.5V

30 pF

DQ

Z

0

= 50

Fig. 1 OUTPUT LOAD EQUIVALENT

50

DQ

3.3v

317

351

Fig. 2 OUTPUT LOAD EQUIVALENT

5 pF

January 22, 199 9

Rev. 1/99

6

Galvantech, Inc. reserves the right to change products or specifications without notice

GVT73128A16

REVOLUTIONARY PINOUT 128K X 16

GALVANTECH

, NC.

NOTES

1.

All voltages referenced to VSS (GND).

V

IH

≤

+6.0V for t

≤

t

RC /2.

Undershoot:

V

IL

≤

-2.0V for t

≤

t

RC /2

I

cc

is given with no output current. I

cc

increases with greater

output loading and faster cycle times.

2.

Overshoot:

3.

4.

This parameter is sampled.

5.

Test conditions as specified with the output loading as shown in

Fig. 1 unless otherwise noted.

6.

Output loading is specified with C

L

=5pF as in Fig. 2. Transition

is measured +500mV from steady state voltage.

At any given temperature and voltage condition,

t

HZCE is less

than

t

LZCE and

t

HZWE is less than

t

LZWE.

7.

8.

WE# is HIGH for READ cycle.

9.

Device is continuously selected. Chip enable and output enables

are held in their active state.

10. Address valid prior to, or coincident with, latest occurring chip

enable.

11.

t

RC

= Read Cycle Time.

12. Chip Enable and Write Enable can initiate and terminate a

WRITE cycle.

13. Capacitance derating applies to capacitance different from the

load capacitance shown in Fig. 1.

14. Typical values are measured at 3.3V, 25

o

C and 20ns cycle time.

DATA RETENTION ELECTRICAL CHARACTERISTICS (L Version Only )

DESCRIPTIO N

CONDITION S

SYMBOL

MIN

TYP

MAX

UNITS

NOTES

Vcc for Retention Data

Data Retention Current

V

DR

I

CCDR

I

CCDR

2

V

CE# >VCC -0.2;

all other inputs < VSS +0.2

or >VCC -0.2;

all inputs static; f= 0

Vcc = 2V

Vcc = 3V

2

3

0.8

1.2

mA

mA

13

13

Chip Deselect to

Data Retention Time

Operation Recovery Time

t

CDR

0

ns

4

t

R

t

RC

ns

4, 11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GVT73128A8SJ-12LI | x8 SRAM |

| GVT73128A8SJ-15 | x8 SRAM |

| GVT73128A8SJ-15I | x8 SRAM |

| GVT73128A8SJ-15L | x8 SRAM |

| GVT73128A8SJ-15LI | x8 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GVT73128A8SJ-12LI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| GVT73128A8SJ-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| GVT73128A8SJ-15I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| GVT73128A8SJ-15L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| GVT73128A8SJ-15LI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。