- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371783 > HCS374HMSR (INTERSIL CORP) Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered PDF資料下載

參數(shù)資料

| 型號: | HCS374HMSR |

| 廠商: | INTERSIL CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| 中文描述: | HC/UH SERIES, 8-BIT DRIVER, TRUE OUTPUT, UUC20 |

| 封裝: | DIE-20 |

| 文件頁數(shù): | 1/10頁 |

| 文件大小: | 175K |

| 代理商: | HCS374HMSR |

358

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright Intersil Corporation 1999

Ordering Information

PART NUMBER

TEMPERATURE RANGE

SCREENING LEVEL

PACKAGE

HCS374DMSR

-55

o

C to +125

o

C

Intersil Class S Equivalent

20 Lead SBDIP

HCS374KMSR

-55

o

C to +125

o

C

Intersil Class S Equivalent

20 Lead Ceramic Flatpack

HCS374D/Sample

+25

o

C

Sample

20 Lead SBDIP

HCS374K/Sample

+25

o

C

Sample

20 Lead Ceramic Flatpack

HCS374HMSR

+25

o

C

Die

Die

HCS374MS

Radiation Hardened Octal D-Type

Flip-Flop, Three-State, Positive Edge Triggered

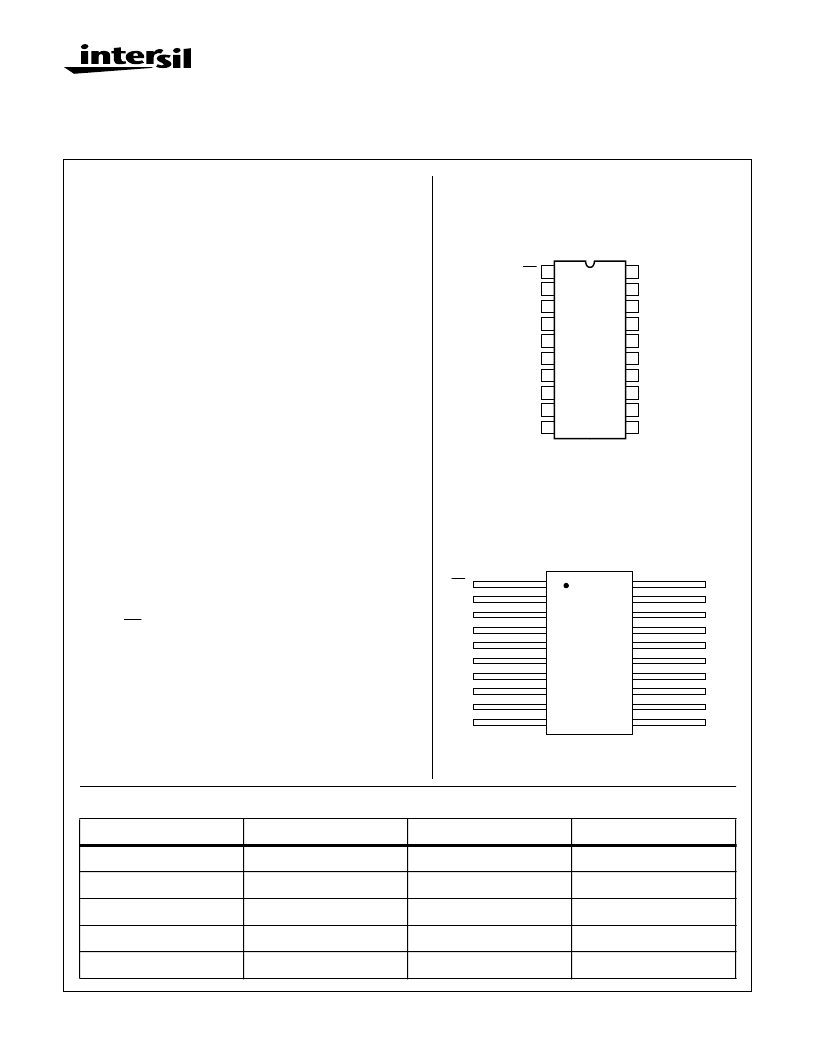

Pinouts

20 LEAD CERAMIC DUAL-IN-LINE

METAL SEAL PACKAGE (SBDIP)

MIL-STD-1835 CDIP2-T20

TOP VIEW

20 LEAD CERAMIC METAL SEAL

FLATPACK PACKAGE (FLATPACK)

MIL-STD-1835 CDFP4-F20

TOP VIEW

11

12

13

14

15

16

17

18

20

19

10

9

8

7

6

5

4

3

2

1

OE

Q0

D0

D1

Q1

Q2

D3

D2

Q3

GND

VCC

D7

D6

Q6

Q7

Q5

D5

D4

Q4

CP

2

3

4

5

6

7

8

9

10

1

20

19

18

17

16

15

14

13

12

11

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

GND

VCC

Q7

D7

D6

Q6

Q5

D5

D4

Q4

CP

Features

3 Micron Radiation Hardened SOS CMOS

Total Dose 200K RAD (Si)

SEP Effective LET No Upsets: >100 MEV-cm

2

/mg

Single Event Upset (SEU) Immunity < 2 x 10

-9

Errors/Bit-

Day (Typ)

Dose Rate Survivability: >1 x 10

12

RAD (Si)/s

Dose Rate Upset >10

10

RAD (Si)/s 20ns Pulse

Latch-Up Free Under Any Conditions

Fanout (Over Temperature Range)

- Bus Driver Outputs - 15 LSTTL Loads

Military Temperature Range: -55

o

C to +125

o

C

Significant Power Reduction Compared to LSTTL ICs

DC Operating Voltage Range: 4.5V to 5.5V

Input Logic Levels

- VIL = 0.3 VCC Max

- VIH = 0.7 VCC Min

Input Current Levels Ii

≤

5

μ

A at VOL, VOH

Description

The Intersil HCS374MS is a Radiation Hardened non-inverting

octal D-type, positive edge triggered flip-flop with three-stateable

outputs. The HCS374MS utilizes advanced CMOS/SOS technol-

ogy. The eight flip-flops enter data into their registers on the

LOW-to-HIGH transition of the clock (CP). Data is also

transferred to the outputs during this transition. The output

enable (OE) controls the three-state outputs and is independent

of the register operation. When the output enable is high, the out-

puts are in the high impedance state.

The HCS374MS utilizes advanced CMOS/SOS technology to

achieve high-speed operation. This device is a member of

radiation hardened, high-speed, CMOS/SOS Logic Family.

The HCS374MS is supplied in a 20 lead Ceramic flatpack

(K suffix) or a SBDIP Package (D suffix).

September 1995

Spec Number

518770

File Number

2470.2

D

相關PDF資料 |

PDF描述 |

|---|---|

| HCS374MS | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered(三態(tài),正邊沿觸發(fā),抗輻射八D觸發(fā)器) |

| HCS374D | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374DMSR | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374K | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374KMSR | Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HCS374K | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374K/SAMPLE | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374KMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374MS | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

| HCS374MS_04 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Octal D-Type Flip-Flop, Three-State, Positive Edge Triggered |

發(fā)布緊急采購,3分鐘左右您將得到回復。