- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370460 > HD404668 (Hitachi,Ltd.) Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit(帶雙音多頻電路的低電壓微計(jì)算機(jī)) PDF資料下載

參數(shù)資料

| 型號(hào): | HD404668 |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit(帶雙音多頻電路的低電壓微計(jì)算機(jī)) |

| 中文描述: | 低電壓如同在微機(jī)芯片的DTMF產(chǎn)生電路(帶雙音多頻電路的低電壓微計(jì)算機(jī)) |

| 文件頁(yè)數(shù): | 10/142頁(yè) |

| 文件大?。?/td> | 894K |

| 代理商: | HD404668 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)

HD404669 Series

10

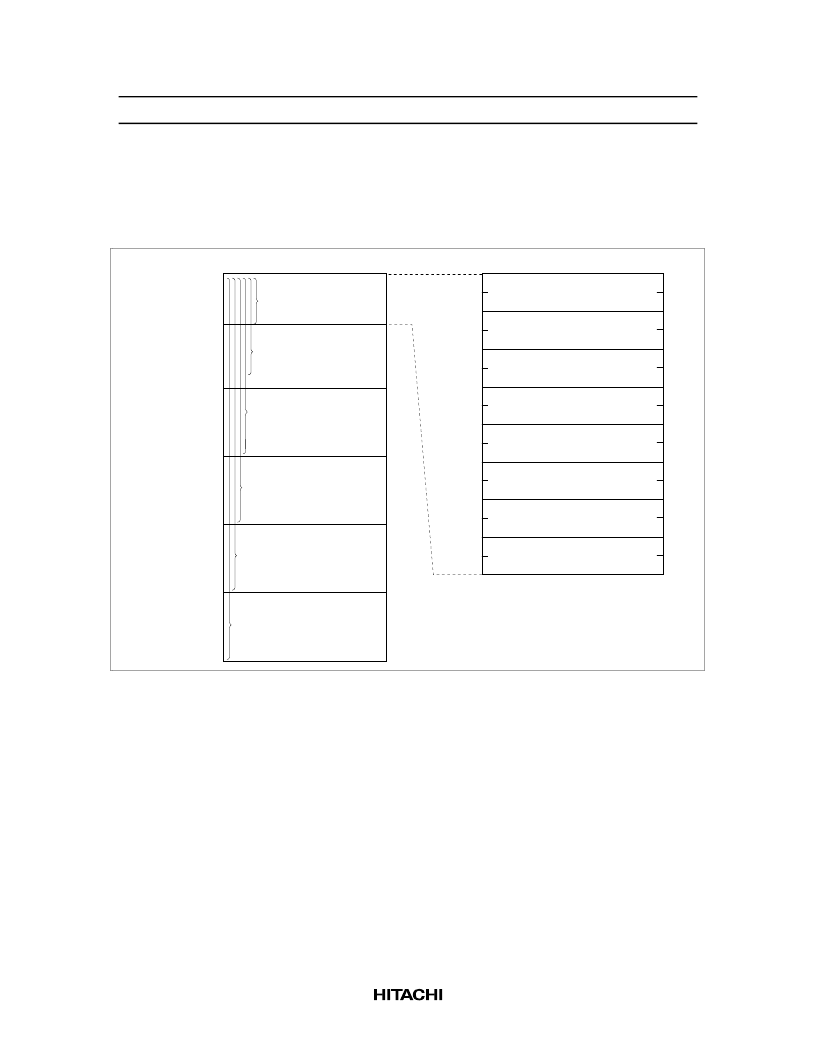

Memory Map

ROM Memory Map

The ROM memory map is shown in figure 1 and described below.

Vector addresses

(16 words)

Zero page subroutine

area (64 words)

Pattern area (4,096 words)

HD404668/HD40A4668

program area (8,192 word)

$000F

$0010

$0FFF

$1000

$3FFF

$003F

$0040

$0000

$0000

$0001

$0002

$0003

$0004

$0005

$0006

$0007

$0008

$0009

$000A

$000B

$000C

$000D

$000E

$000F

ROM address

JMPL instruction

(Jump to reset, stop mode clearance

routine)

JMPL instruction

(Jump to

INT

0

interrupt handling

routine)

JMPL instruction

(Jump to

INT

1

interrupt handling

routine)

(Jump to timer A interrupt handling

routine)

JMPL instruction

(Jump to INT

2

interrupt handling

routine)

JMPL instruction

(Jump to timer C, INT

3

interrupt

handling routine)

JMPL instruction

(Jump to timer D, INT

4

interrupt

handling routine)

ROM address

HD4046612/HD40A46612

program area (12,288 words)

HD404669/HD40A4669/

HCD404669/HD407A4669

program area (16,384 words)

$1FFF

$2000

$2FFF

$3000

JMPL instruction

(Jump to serial 1 routine)

Figure 1 ROM Memory Map

Vector Address Area ($0000–$000F):

Reserved for JMPL instructions that branch to the start addresses

of the reset and interrupt routines. After MCU reset or an interrupt, program execution continues from the

vector address.

Zero-Page Subroutine Area ($0000–$003F):

Reserved for subroutines. The program branches to a

subroutine in this area in response to the CAL instruction.

Pattern Area ($0000–$0FFF):

Contains ROM data that can be referenced with the P instruction.

Program Area ($0000–$1FFF: HD404668, HD40A4668; $0000–$2FFF: HD4046612, HD40A46612;

$0000–$3FFF: HD404669, HD40A4669, HD407A4669, HCD404669):

Used for program coding.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HD404669 | Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit(帶雙音多頻電路的低電壓微計(jì)算機(jī)) |

| HD407A4669 | Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit(帶雙音多頻電路的低電壓微計(jì)算機(jī)) |

| HD404719FS | Five timer/counters |

| HD404439FS | Five timer/counters |

| HD4074719FS | Five timer/counters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HD404668H | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit |

| HD404669 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit |

| HD404669H | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:Low-Voltage AS Microcomputers with On-Chip DTMF Generation Circuit |

| HD404669SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HD404676H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。