- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296194 > HPC46100 (National Semiconductor Corporation) HPC46100 High-Performance microController with DSP Capability PDF資料下載

參數(shù)資料

| 型號: | HPC46100 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | HPC46100 High-Performance microController with DSP Capability |

| 中文描述: | HPC46100高性能微控制器與DSP處理能力 |

| 文件頁數(shù): | 15/32頁 |

| 文件大?。?/td> | 436K |

| 代理商: | HPC46100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

Timer Overview (Continued)

the timer and operation will continue as in the PWM mode

Alternately an interrupt from the RnB load can be used to

branch to a routine that would set the timer into mode 3

waiting for the trigger for another pulse

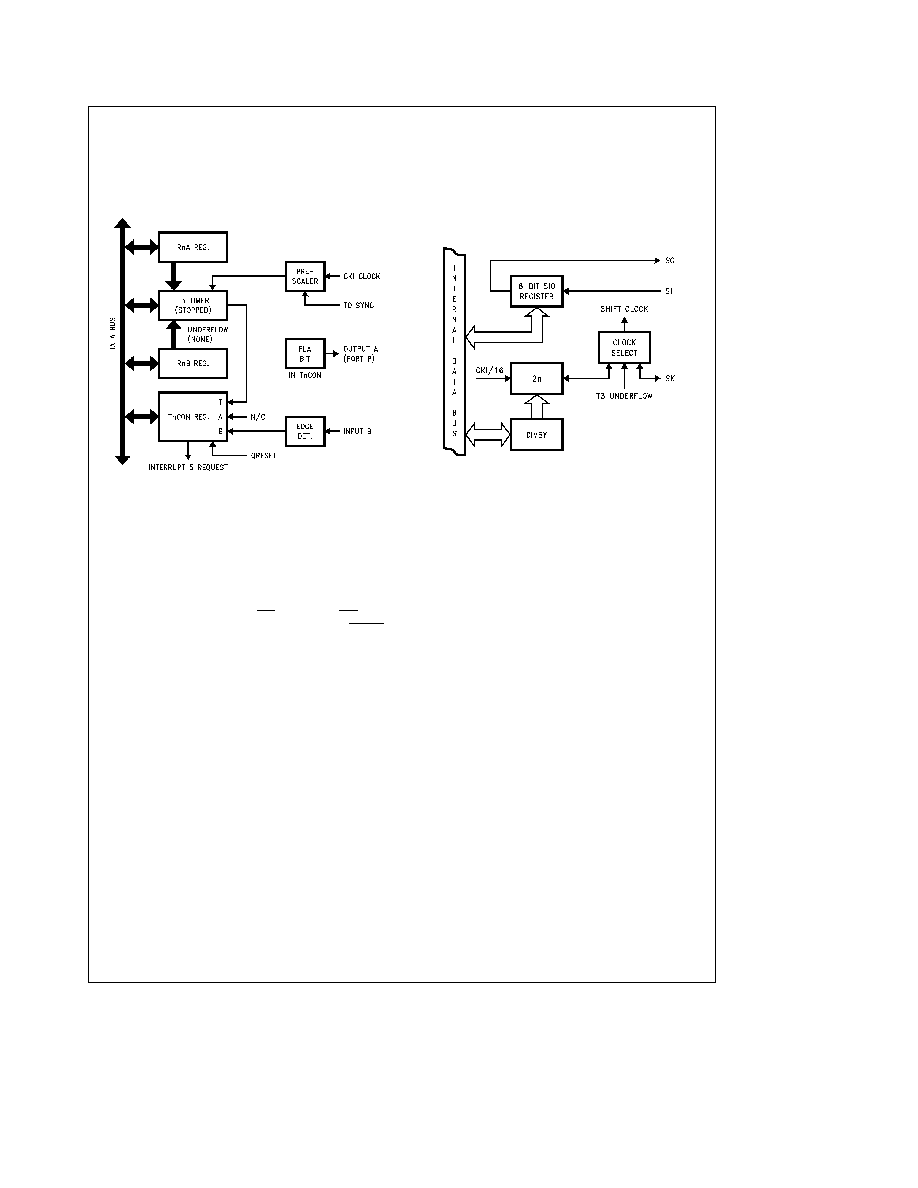

Figure 25 shows a

block diagram of the timer in this mode

TLDD11289 – 27

FIGURE 25 Port OutputExternally Triggered PWM

WATCHDOG LOGIC

The WATCHDOG Logic monitors the operations taking

place and signals upon the occurrence of any illegal activity

The illegal conditions that trigger the WATCHDOG logic are

potentially infinite loops Should the WATCHDOG register

not be written to before Timer T0 overflows twice or more

often than once every 4096 counts an infinite loop condi-

tion is assumed to have occurred Any illegal condition

forces the WATCHDOG Output (WO) pin low The WO pin is

an open drain output and can be connected to the RESET

or NMI inputs or to the users external logic

MICROWIREPLUS

MICROWIREPLUS is used for synchronous serial data

communications and has an 8-bit parallel-loaded serial shift

register using SI as the input and SO as the output SK is

the clock for the serial shift register (SIO) The SK clock

signal can be provided by an internal or external source

The internal clock rate is programmable by the DIVBY regis-

ter A DONE flag indicates when the data shift is completed

The MICROWIREPLUS capability enables it to interface

with any of National Semiconductor’s MICROWIRE periph-

erals (ie AD converters display drivers EEPROMs)

MICROWIREPLUS OPERATION

The HPC46100 can enter the MICROWIREPLUS mode as

the master or a slave A control bit in the IRCD register

determines whether the HPC46100 is the master or slave

The shift clock is generated when the HPC46100 is config-

ured as a master An externally generated shift clock on the

SK pin is used when the HPC46100 is configured as a slave

When the HPC46100 is a master the DIVBY register pro-

grams the frequency of the SK clock The DIVBY register

allows the SK clock frequency to be programmed in 15 se-

lectable steps from 64 Hz to 1 MHz with CKI at 160 MHz

The contents of the SIO register may be accessed through

any of the memory access instructions Data waiting to be

transmitted in the SIO register is clocked out on the falling

edge of the SK clock Serial data on the SI pin is clocked in

on the rising edge of the SK clock

TLDD11289 – 28

FIGURE 26 MICROWIREPLUS

HPC46100 UART

The HPC46100 contains a software programmable UART

The UART (see

Figure 27 ) consists of a transmit shift regis-

ter a receiver shift register and five addressable registers

as follows a transmit buffer register (TBUF) a receiver buff-

er register (RBUF) a UART control and status register

(ENU) a UART receive control and status register (ENUR)

and a UART interrupt and clock source register (ENUI) The

ENU register contains flags for transmit and receive func-

tions this register also determines the length of the data

frame (7 8 or 9 bits) and the value of the ninth bit in trans-

mission The ENUR register flags framing parity and data

overrun errors while the UART is receiving Other functions

of the ENUR register include saving the ninth bit received in

the data frame reporting receiving and transmitting status

and enabling or disabling the UART’s Attention Mode of

operation

The determination of an internal or external clock source is

done by the ENUI register as well as selecting the number

of stop bits (

1 1

or 2 stop bits) selecting between the

synchronous or asynchronous mode and enabling or dis-

abling transmit and receive interrupts The clock inputs to

the Transmitter and Receiver sections of the UART can be

individually selected to come from either an off-chip source

on the CKX pin or one of the two on-chip sources The

Divide-By (DIVBY) Register provides upward compatibility

from earlier HPC family members and the most flexible and

accurate on-chip clocking is provided by the Baud Rate

Generator (BRG)

22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC46400EV2 | High-Performance Communications MicroController |

| HPH-12/30-D48PBHL2-C | 1-OUTPUT 360 W DC-DC REG PWR SUPPLY MODULE |

| HPSTP-19-5000-01 | INTERCONNECTION DEVICE |

| HPT-136-01-SM-D-RA | 72 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| HPT-153-01-L-D-RA | 106 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC46100VF40 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:HPC46100 High-Performance microController with DSP Capability |

| HPC46100VHG40 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| HPC46104 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High-Performance microController with A/D |

| HPC46104E20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| HPC46104E30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。