- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370686 > HS9-82C37ARH (Intersil Corporation) Radiation Hardened CMOS High Performance Programmable DMA Controller PDF資料下載

參數(shù)資料

| 型號(hào): | HS9-82C37ARH |

| 廠商: | Intersil Corporation |

| 英文描述: | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| 中文描述: | 輻射加固的CMOS高性能可編程DMA控制器 |

| 文件頁(yè)數(shù): | 26/28頁(yè) |

| 文件大?。?/td> | 253K |

| 代理商: | HS9-82C37ARH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)

26

HS-82C37ARH

Application Information

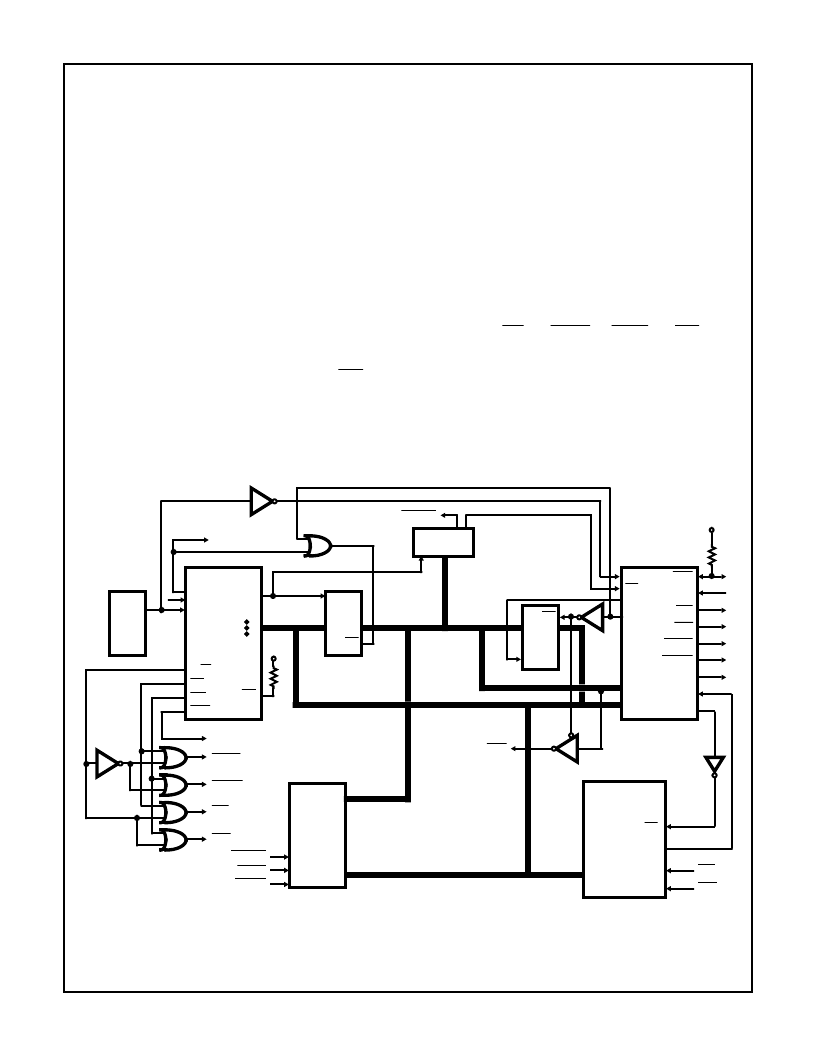

Figure 12 shows an application for a DMA system utilizing

the HS-82C37ARH DMA controller and the HS-80C86RH

Microprocessor. In this application, the HS-82C37ARH DMA

controller is used to improve system performance by allow-

ing an I/O device to transfer data directly to or from system

memory.

Components

The system clock is generated by the HS-82C85RH clock

controllers generator and is inverted to meet the clock high

and low times required by the HS-82C37ARH DMA control-

ler. The four OR gates are used to support the HS-80C86RH

Microprocessor in minimum mode by producing the control

signals used by the processor to access memory or I/O. A

decoder is used to generate chip select for the DMA control-

ler and memory. The HS-82C37ARH multiplexes the most

significant bits of the address on its data outputs (DB0 - 7),

so the 82C82 octal latch is used to demultiplex the address.

A three-state inverter is used to generate the BHE signal

using the A0 output of the HS-82C37ARH. Hold Acknowl-

edge (HLDA) and Address Enable (AEN) are “ORed”

together and used to deactivate the microprocessors 82C82

transceiver to insure that the DMA controller does not have

bus contention with the microprocessor.

Operation

A DMA request (DREQ) is generated by the I/O device. After

receiving the DMA request, the DMA controller will issue a

Hold Request (HRQ) to the processor. The system busses

are not released to the DMA controller until a Hold Acknowl-

edge (HLDA) signal is returned to the DMA controller from

the HS-80C86RH processor. After the Hold Acknowledge

has been received, addresses and control signals are gener-

ated by the DMA controller to accomplish the DMA transfers.

Data is transferred directly from the I/O device to memory (or

vice versa) with IOR and MEMW (or MEMR and IOW) being

active. Note that data is not read into or driven out of the

DMA controller in I/O-to-Memory or Memory-to-I/O data

transfers.

FIGURE 12. APPLICATION FOR DMA SYSTEM

STB

OE

82C82

CLK

CS

ADSTB

AEN

A0-7

DB0-7

EOP

IOW

MEMR

MEMW

HRQ

DREQ0

DACK0

IOR

HLDA

DECODER

MEMCS

CLK

HS-82C85RH

HLDA

HLDA

HRQ

ALE

AD0

AD15

VDD

MN/MX

M/10

RD

WR

BHE

MEMW

IOR

IOW

MEMR

MEMR

MEMW

MEMCS

MEMORY

HS-80C86RH

DATA BUS

ADDRESS BUS

DATA BUS

STB

OE

82C82

ADDRESS

BUS

BHE

A0

VDD

CS

DREQ

I/O

DEVICE

IOR

IOW

HS-82C37ARH

Spec Number

518058

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS9-9808RH | Converter IC |

| HS1-9808RH | Converter IC |

| HS9-RTX2010RH8 | 16-Bit Microcontroller |

| HS9149A | HS9149A |

| HS9516B-4 | Analog-to-Digital Converter, 16-Bit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS9-82C37ARH/SAMPLE | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C37ARH-8 | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C37ARH-Q | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C54RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Programmable Interval Timer |

| HS9-82C54RH-8 | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24PIN CFLATPACK - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。