- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371900 > HT36A0(48DIP) Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | HT36A0(48DIP) |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 6/21頁(yè) |

| 文件大小: | 229K |

| 代理商: | HT36A0(48DIP) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

HT36A0

Rev. 1.00

6

September 3, 2002

Function Description

Execution flow

The system clock for the HT36A0 is derived from either

a crystal or an RC oscillator. The oscillator frequency di-

vided by 2 is the system clock for the MCU and it is inter-

nally divided into four non-overlapping clocks. One

instruction cycle consists of four system clock cycles.

Instruction fetching and execution are pipelined in such

a way that a fetch takes one instruction cycle while de-

coding and execution takes the next instruction cycle.

However, the pipelining scheme causes each instruc-

tion to effectively execute in one cycle. If an instruction

changes the program counter, two cycles are required

to complete the instruction.

Program counter

PC

The 13-bit program counter (PC) controls the sequence

in which the instructions stored in program ROM are ex-

ecuted and its contents specify a maximum of 8192 ad-

dresses for each bank.

After accessing a program memory word to fetch an in-

struction code, the contents of the program counter are

incremented by one. The program counter then points

to the memory word containing the next instruction

code.

When executing a jump instruction, conditional skip ex-

ecution, loading PCL register, subroutine call, initial re-

set, internal interrupt, external interrupt or return from

subroutine, the PC manipulates the program transfer by

loading the address corresponding to each instruction.

Theconditionalskipisactivatedbyinstruction.Oncethe

condition is met, the next instruction, fetched during the

current instruction execution, is discarded and a dummy

cyclereplacesittoretrievetheproperinstruction.Other-

wise proceed with the next instruction.

The lower byte of the program counter (PCL) is a read-

able and writeable register (06H). Moving data into the

PCL performs a short jump. The destination will be

within 256 locations.

Once a control transfer takes place, an additional

dummy cycle is required.

Program ROM

HT36A0 provides 16 address lines WA[15:0] to read the

Program ROM which is up to 1M bits, and is commonly

used for the wavetable voice codes and the program

memory. It provides two address types, one type is for

program ROM, which is addressed by a bank pointer

PF2~0 and a 13-bit program counter PC 12~0; and the

'

'

' !

'

'

'

' !

'

'

'

' !

'

(

6

. 1 + " ' . ,

/

# ;

6

. 1 + " ' . ,

/

(

6

. 1 + " ' . ,

<

/

# ;

6

. 1 + " ' . ,

/

(

6

. 1 + " ' . ,

<

/

# ;

6

. 1 + " ' . ,

<

/

<

<

" 7

= .

3 6 : . 3 0 .

, " 7

= .

3 6 :

/

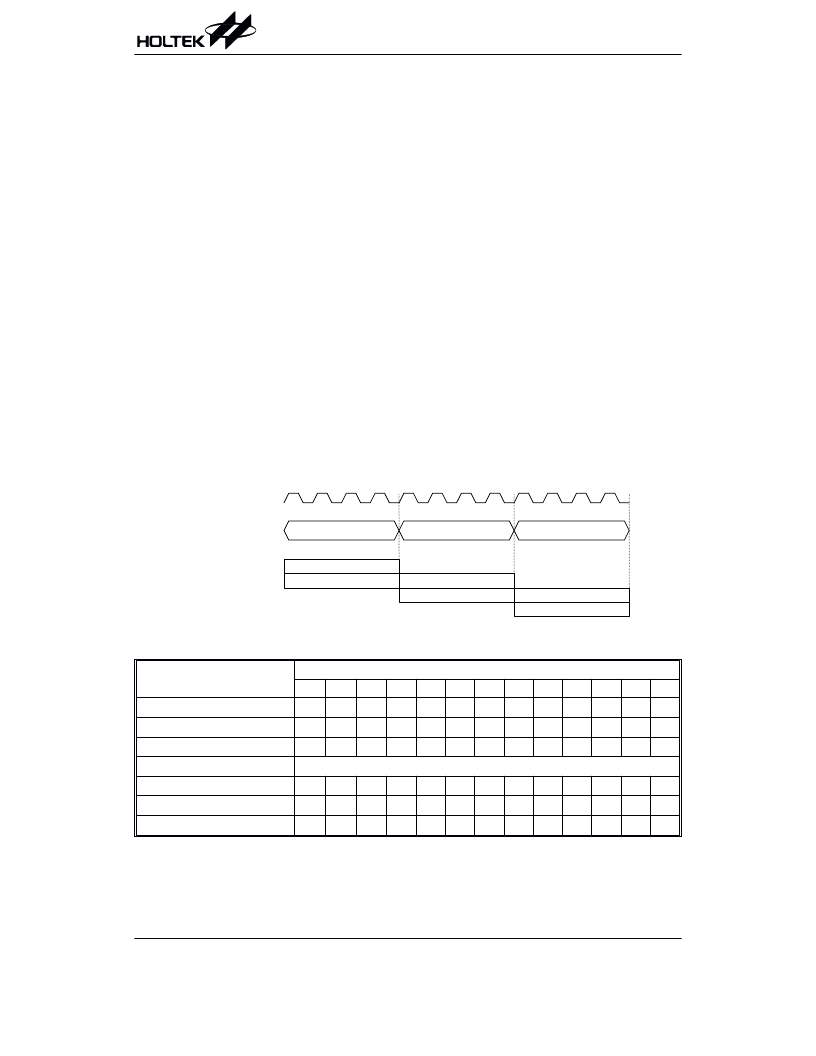

Execution flow

Mode

Program Counter

*12

*11

*10

*9

*8

*7

*6

*5

*4

*3

*2

*1

*0

Initial Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

Timer/event Counter 0 Overflow

0

0

0

0

0

0

0

0

0

1

0

0

0

Timer/event Counter 1 Overflow

0

0

0

0

0

0

0

0

0

1

1

0

0

Skip

PC+2

Loading PCL

*12

*11

*10

*9

*8

@7

@6

@5

@4

@3

@2

@1

@0

Jump, Call Branch

#12

#11

#10

#9

#8

#7

#6

#5

#4

#3

#2

#1

#0

Return From Subroutine

S12

S11

S10

S9

S8

S7

S6

S5

S4

S3

S2

S1

S0

Program counter

Note:

*12~*0: Bits of Program Counter

@7~@0: Bits of PCL

#12~#0: Bits of Instruction Code

S12~S0: Bits of Stack Register

@7~@0: Bits of PCL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT3820(16DIP) | Sound Generator Circuit |

| HT3820(16SOP) | Sound Generator Circuit |

| HT3820A | Sound Generator Circuit |

| HT3820A(TO92A) | Analog IC |

| HT3820B | Sound Generator Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT36A1 | 制造商:HOLTEK 制造商全稱(chēng):Holtek Semiconductor Inc 功能描述:Music Synthesizer 8-Bit MCU |

| HT36A2 | 制造商:HOLTEK 制造商全稱(chēng):Holtek Semiconductor Inc 功能描述:8-Bit Music Synthesizer MCU |

| HT36A3 | 制造商:HOLTEK 制造商全稱(chēng):Holtek Semiconductor Inc 功能描述:8-Bit Music Synthesizer MCU |

| HT36A4 | 制造商:HOLTEK 制造商全稱(chēng):Holtek Semiconductor Inc 功能描述:Music Synthesizer 8-Bit MCU |

| HT36A4_07 | 制造商:HOLTEK 制造商全稱(chēng):Holtek Semiconductor Inc 功能描述:Music Synthesizer 8-Bit MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。