- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370799 > HYPERPHY HyperPHY transceiver cores Gflx Standard HyperPHY PDF資料下載

參數(shù)資料

| 型號(hào): | HYPERPHY |

| 英文描述: | HyperPHY transceiver cores Gflx Standard HyperPHY |

| 中文描述: | HyperPHY收發(fā)器內(nèi)核Gflx標(biāo)準(zhǔn)HyperPHY |

| 文件頁(yè)數(shù): | 1/2頁(yè) |

| 文件大小: | 72K |

| 代理商: | HYPERPHY |

F E AT U R E S

Data rates from 528 Mbps to 800

Mbps

Supports SPI-4.2 and SFI-4 standards

8-bit parallel word with associated

clock

Up to 128 full duplex channels

allowed on a single ASIC

LVDS buffers with on-chip termination

resistors

Physically separate serializer and

de-serializer cores

Typical 55 mW per full duplex chan-

nel at 622 Mbps

Allows at-speed built-in-self-test of full

transmit and receive/clock recovery

functions

Able to receive data reliably even

with long sequences of data without

transitions

Receiver channel-to-channel de-skew

Produced in LSI Logic Gflx technolo-

gy (0.13 micron CMOS)

1.2V supply

B E N E F I T S

Modular building blocks allow for

flexible architectures with an ASIC-

friendly design approach

Separate serializer and de-serializer

cores allow for data flow architectures

Supports OC-12/STM-4 data rate

with up to two levels of forward error

correction

O V E R V I E W

HyperPHY

TM

is an LSI Logic CoreWare

transceiver technology family

designed for broadband and networking applications for extremely high band-

width CMOS ASICs.

HyperPHY transceiver technology includes a full clock recovery mechanism

that permits the recovery of clock and data from a data stream alone.

Communication on HyperPHY channels is possible over a variety of physical

media, including copper cable and printed circuit board traces with high speed

backplane connectors

Gflx

T M

S TA N D A R D H Y P E R P H Y D E S C R I P T I O N

Gflx

TM

Standard HyperPHY represents the fourth generation of a continuing

transceiver technology family. The HyperPHY methodology allows for the con-

struction of transceiver architectures in an ASIC methodology.

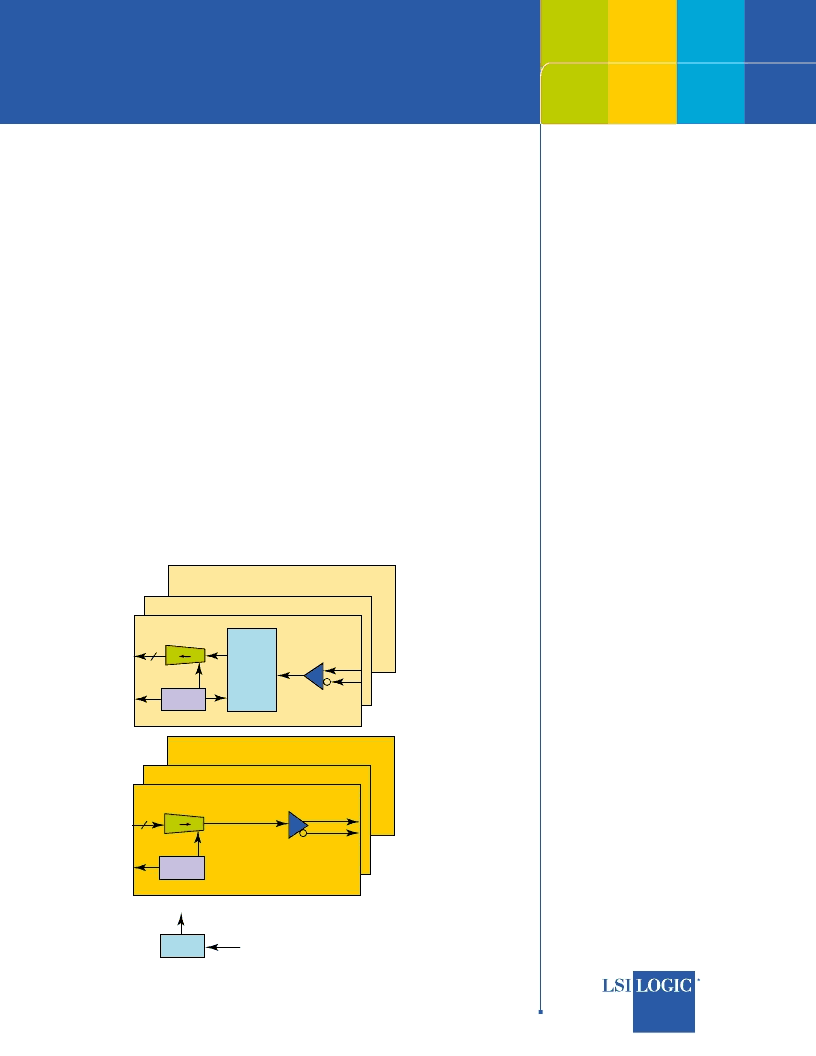

The cores consist of a serializer, a de-serializer with clock and data recov-

ery, and a low-jitter PLL. These cores, shown in Figure 1 as TX, RX and PLL,

respectively, are combined into sub-systems per customer specifications. Figure

1 shows a generic full duplex subsystem, with 32 independent receive channels

and 32 independent transmit channels, all serviced by a single PLL.

HyperPHY

Transceiver Cores

G

flx

Standard HyperPHY

Figure 1: Block diagram of ASIC subsystem using Gflx Standard HyperPHY

RX Channel 32

RX Channel 2

Receive Data Word

20

P

S

Control

Clock

and

Data

Recovery

Serial

LVDS

Receiver

High Speed

Serial RX Data

Receive Data Word Clock

(8 bit word)

RX Channel 1

TX Channel 32

TX Channel 2

Transmit Data Word

20

P

Control

Serial

LVDS

Driver

High Speed

Serial TX Data

Transmit Data Word Clock

(8 bit word)

TX Channel 1

PLL

Reference Clock

S

PLL Clock To All Channels

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYR-1559 | High Voltage Breakdown |

| HYR1559 | High Voltage Breakdown |

| HYR 1612830G | 256MB Rambus RIMM Modules(256M位 Rambus RIMM 模塊) |

| HYR 163230G | 64MB Rambus RIMM Modules(64M位 Rambus RIMM 模塊) |

| HYR 186420G | 144MB Rambus RIMM Modules(144M位 Rambus RIMM 模塊) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYPNOTIC RGB | 制造商:American DJ 功能描述:Red Green Blue Web Pattern DMX Laser Projector |

| HYPS-01712 | 制造商:HYLEC 功能描述:TERMINAL BLOCK PLUG & SKT 12WAY 制造商:HYLEC 功能描述:TERMINAL BLOCK, PLUG & SKT, 12WAY 制造商:HYLEC 功能描述:TERMINAL BLOCK, PLUG & SKT, 12WAY; Connector Type:Terminal Block; Connector Mounting:Cable; Pitch Spacing:9.6mm; No. of Contacts:12; Contact Plating:Nickel; Contact Material:Brass ;RoHS Compliant: Yes |

| HYR 1003 | 制造商:Aleph America Corporation 功能描述: |

| HYR 2001/2031 | 制造商:Aleph America Corporation 功能描述: |

| HYR 2031 | 制造商:Aleph America Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。