- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370802 > HYS64D16000GDL-8-B (INFINEON TECHNOLOGIES AG) Network Cable Assembly; Connector Type A:T568A/B Modular Plug; Connector Type B:T568A/B Modular Plug; Cable Length:15ft; Approval Categories:Augmented Category 6 standards; cord color per TIA/EIA-606 standard RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號: | HYS64D16000GDL-8-B |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | Network Cable Assembly; Connector Type A:T568A/B Modular Plug; Connector Type B:T568A/B Modular Plug; Cable Length:15ft; Approval Categories:Augmented Category 6 standards; cord color per TIA/EIA-606 standard RoHS Compliant: Yes |

| 中文描述: | 200引腳小外型雙列直插內(nèi)存模塊 |

| 文件頁數(shù): | 20/31頁 |

| 文件大小: | 777K |

| 代理商: | HYS64D16000GDL-8-B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

8

8

10

10

0.6

0.6

2.5

Data Sheet

20

V1.2, 2003-08

HYS64D[1600x/32020]GDL–[5/6/7/8]–B

Small Outline DDR SDRAM Modules

AC Characteristics

9) The maximum limit for this parameter is not a device limit. The device operates with a greater value for this parameter, but

system performance (bus turnaround) degrades accordingly.

10) Fast slew rate

≥

1.0 V/ns , slow slew rate

≥

0.5 V/ns and < 1 V/ns for command/address and CK & CK slew rate > 1.0 V/

ns, measured between

V

OH(ac)

and

V

OL(ac)

.

11) For each of the terms, if not already an integer, round to the next highest integer.

t

CK

is equal to the actual system clock

cycle time.

12) A maximum of eight Autorefresh commands can be posted to any given DDR SDRAM device.

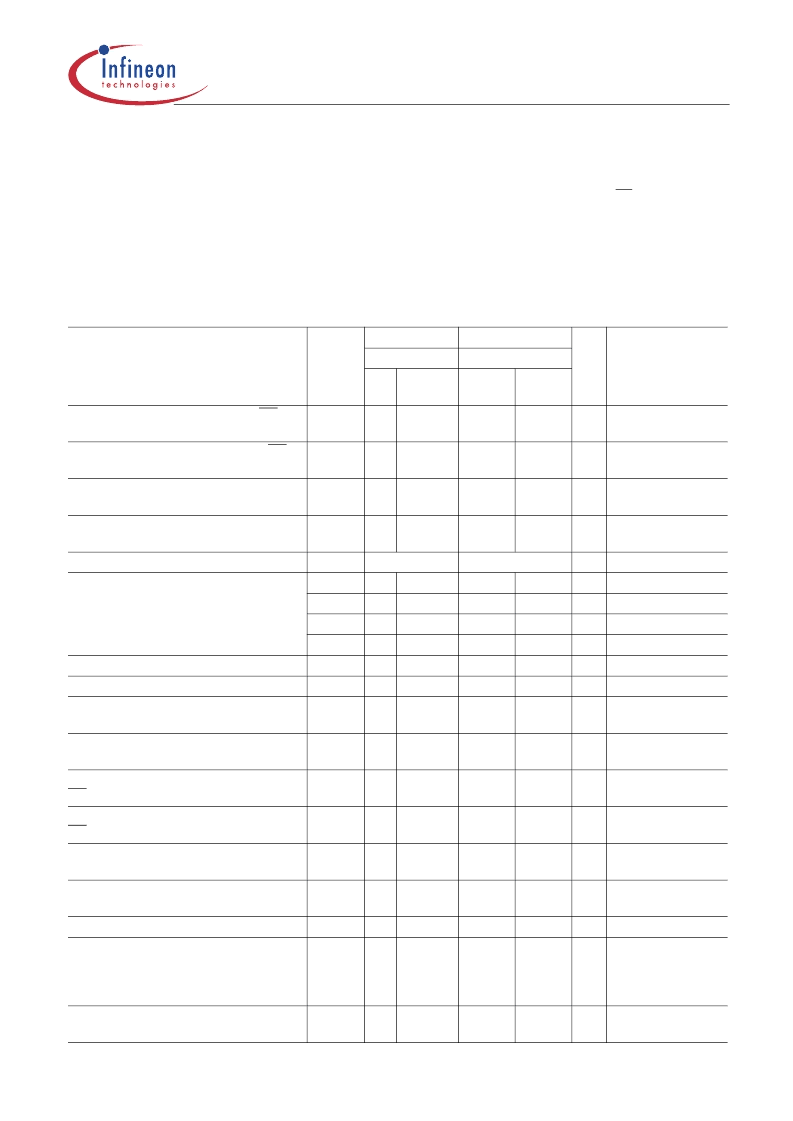

Table 12

Parameter

AC Timing - Absolute Specifications –8/–7

Symbol

–8

–7

Unit Note/

Test Condition

1)

DDR200

Min

.

–

0.8

–

0.8

0.4

5

0.4

5

min. (

t

CL

,

t

CH

)

12

12

12

12

—

—

—

DDR266A

Min.

Max.

Max.

DQ output access time from CK/CK

t

AC

+0.8

–0.75

+0.75

ns

2)3)4)5)

DQS output access time from CK/CK

t

DQSCK

+0.8

–0.75

+0.75

ns

2)3)4)5)

CK high-level width

t

CH

0.55

0.45

0.55

t

CK

2)3)4)5)

CK low-level width

t

CL

0.55

0.45

0.55

t

CK

2)3)4)5)

Clock Half Period

Clock cycle time

t

HP

t

CK3

t

CK2.5

t

CK2

t

CK1.5

t

DH

t

DS

t

IPW

min. (

t

CL

,

t

CH

)

ns

ns

ns

ns

ns

ns

ns

ns

2)3)4)5)

7

7

7.5

—

0.5

0.5

2.2

12

12

12

—

—

—

—

CL = 3.0

2)3)4)5)

CL = 2.5

2)3)4)5)

CL = 2.0

2)3)4)5)

CL = 1.5

2)3)4)5)

2)3)4)5)

DQ and DM input hold time

DQ and DM input setup time

Control and Addr. input pulse width

(each input)

DQ and DM input pulse width (each

input)

Data-out high-impedance time from CK/

CK

Data-out low-impedance time from CK/

CK

Write command to 1

st

DQS latching

transition

DQS-DQ skew (DQS and associated

DQ signals)

Data hold skew factor

DQ/DQS output hold time

2)3)4)5)

2)3)4)5)6)

t

DIPW

2.0

—

1.75

—

ns

2)3)4)5)6)

t

HZ

–

0.8

–

0.8

0.7

5

—

+0.8

–0.75

+0.75

ns

2)3)4)5)7)

t

LZ

+0.8

–0.75

+0.75

ns

2)3)4)5)7)

t

DQSS

1.25

0.75

1.25

t

CK

2)3)4)5)

t

DQSQ

+0.6

—

+0.5

ns

2)3)4)5)

t

QHS

t

QH

—

t

HP

–

t

QH

S

0.3

5

1.0

—

—

t

HP

–

t

QHS

0.75

—

ns

ns

2)3)4)5)

2)3)4)5)

DQS input low (high) pulse width (write

cycle)

t

DQSL,H

—

0.35

—

t

CK

2)3)4)5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS64D16000GU-7-A | Unbuffered DDR SDRAM-Modules |

| HYS72D16000GU-7-A | Unbuffered DDR SDRAM-Modules |

| HYS64D32020GU-7-A | Unbuffered DDR SDRAM-Modules |

| HYS72D32020GU-7-A | Unbuffered DDR SDRAM-Modules |

| HYS64D16000GU-8-A | Unbuffered DDR SDRAM-Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64D16000GU-7-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Unbuffered DDR SDRAM-Modules |

| HYS64D16000GU-8-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Unbuffered DDR SDRAM-Modules |

| HYS64D16000HDL-6-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:200-Pin Small Outline Dual-In-Line Memory Modules |

| HYS64D16001GDL-6-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:200-Pin Small Outline Dual-In-Line Memory Modules |

| HYS64D16001GDL-7-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:200-Pin Small Outline Dual-In-Line Memory Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。