- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370803 > HYS64T64020HDL-5-A (INFINEON TECHNOLOGIES AG) 200-Pin Small Outline Dual-In-Line Memory Module PDF資料下載

參數(shù)資料

| 型號: | HYS64T64020HDL-5-A |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 200-Pin Small Outline Dual-In-Line Memory Module |

| 中文描述: | 200引腳小外型雙列內(nèi)存模組 |

| 文件頁數(shù): | 6/31頁 |

| 文件大小: | 955K |

| 代理商: | HYS64T64020HDL-5-A |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

Preliminary

Double-Data-Rate-Two SDRAM Micro-DIMM

DDR2 MDIMM

HYS64T32000[H/K/L]M–[3.7/5]–A

HYS64T64020[H/K/L]M–[3.7/5]–A

Data Sheet

6

Rev. 0.6, 2004-06

03242004-2CBE-IJ2X

1

Overview

This chapter gives an overview of the Double-Data-Rate-Two SDRAM Micro-DIMM product family and describes

its main characteristics.

1.1

Features

214-pin PC2-4200 and PC2-3200 DDR2 SDRAM

memory modules for use as main memory when

installed in systems such as mobile personal

computers.

32M

×

64 and 64M

×

64 module organisation and

32M

×

16 chip organisation

JEDEC standard Double-Data-Rate-Two

Synchronous DRAMs (DDR2 SDRAM) with a single

+ 1.8 V (± 0.1 V) power supply

Built with 512Mb DDR2 SDRAMs in P-TFBGA-84-2

chipsize packages

Programmable CAS Latencies (3, 4 and 5), Burst

Length (8 & 4) and Burst Type

Burst Refresh, Distributed Refresh and Self Refresh

All inputs and outputs SSTL_1.8 compatible

OCD (Off-Chip Driver Impedance Adjustment) and

ODT (On-Die Termination)

Serial Presence Detect with E

2

PROM

Micro-DIMM Dimensions (nominal) : 30 mm high,

54.0 mm wide

Based on JEDEC standard reference layouts Raw

Card “A” & “B”

2-piece type Mezzanine Socket with 0,4 mm

contact centers

1.2

Description

The

[3.7/5]–A module family are low profile Unbuffered

Micro-DIMM modules “MDIMMs” with 30,0 mm height

based on DDR2 technology. DIMMs are available as

32M

×

64 and 64M

×

64 organisation and density,

intended for mounting into 214-pin mezzanine

connector sockets.

INFINEON

HYS64T[3200/6402]0[H/K/L]M–

The memory array is designed with 512Mb Double-

Data-Rate-Two

(DDR2)

Decoupling capacitors are mounted on the PCB board.

The DIMMs feature serial presence detect based on a

serial E

2

PROM device using the 2-pin I

2

C protocol. The

first 128 bytes are programmed with configuration data

and are write protected; the second 128 bytes are

available to the customer.

Synchronous

DRAMs.

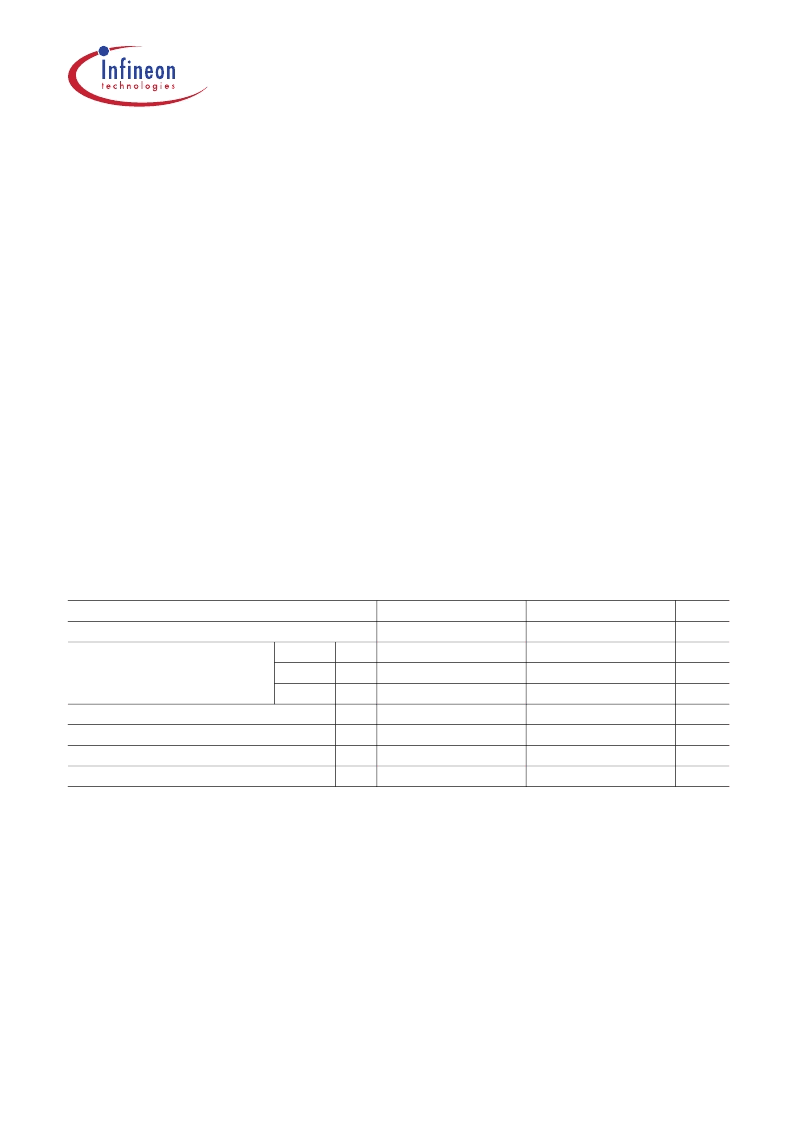

Table 1

Product Type Speed Code

Speed Grade

max. Clock Frequency

Performance

–3.7

PC2–4200 4–4–4

266

266

200

15

15

45

60

–5

PC2–3200 3–3–3

200

200

200

15

15

45

60

Units

—

MHz

MHz

MHz

ns

ns

ns

ns

@CL5

@CL4

@CL3

f

CK5

f

CK4

f

CK3

t

RCD

t

RP

t

RAS

t

RC

min. RAS-CAS-Delay

min. Row Precharge Time

min. Row Active Time

min. Row Cycle Time

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS64T64020HM | 3.5GHZ 10W GAAS NI360HF |

| HYS64T64020KM | Double-Data-Rate-Two SDRAM Micro-DIMM |

| HYS64T64020KM-37-A | Double-Data-Rate-Two SDRAM Micro-DIMM |

| HYS64T64020KM-5-A | Double-Data-Rate-Two SDRAM Micro-DIMM |

| HYS64T64020LM | Double-Data-Rate-Two SDRAM Micro-DIMM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64T64020HDL-5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:200 Pin Small-Outlined DDR2 SDRAMs Modules |

| HYS64T64020HM | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:214-Pin Micro-DIMM-DDR2-SDRAM Modules |

| HYS64T64020HM-3.7-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:214-Pin Micro-DIMM-DDR2-SDRAM Modules |

| HYS64T64020HM-37-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Double-Data-Rate-Two SDRAM Micro-DIMM |

| HYS64T64020HM-3S-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:214-Pin Micro-DIMM-DDR2-SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。