- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370809 > HYS72T128000HR-5-A (INFINEON TECHNOLOGIES AG) DDR2 Registered Memory Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72T128000HR-5-A |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | DDR2 Registered Memory Modules |

| 中文描述: | 注冊的DDR2內(nèi)存模塊 |

| 文件頁數(shù): | 17/33頁 |

| 文件大小: | 936K |

| 代理商: | HYS72T128000HR-5-A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

HYS72T[256/128/64][0/2][0/2]0[G/H]R-[5/3.7]-A

Registered DDR2 SDRAM Modules

Data Sheet

Preliminary

17

Rev. 0.85, 2004-04

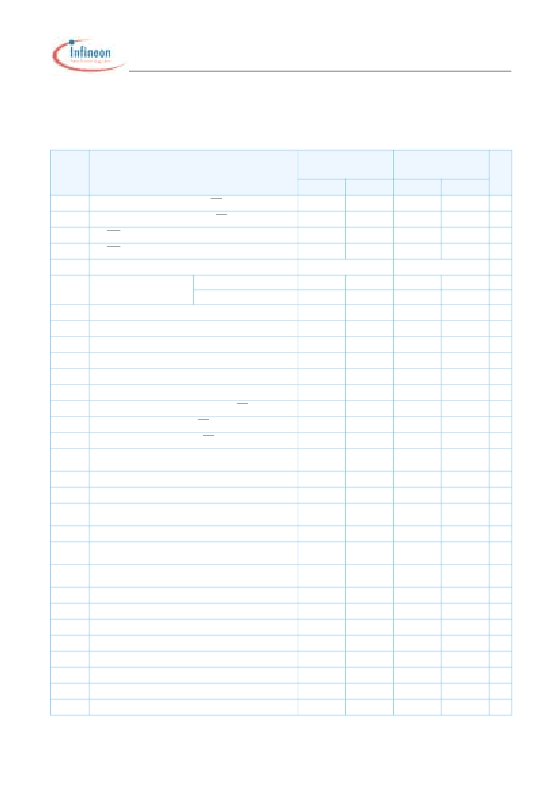

5.0 Electrical Characteristics & AC Timings

5.1 AC Timing Parameter by Speed Grade

(Component level data, for reference only)

Symbol

Parameter

-5

DDR2-400

-3.7

DDR2-533

Unit

Min

Max

Min

Max

t

AC

DQ output access time from CK / CK

600

+

600

-500

+500

ps

t

DQSCK

t

CH

t

CL

t

HP

DQS output access time from CK / CK

500

+

500

450

+

450

ps

CK, CK high-level width

0.45

0.55

0.45

0.55

t

CK

CK, CK low-level width

0.45

0.55

0.45

0.55

t

CK

Clock Half Period

min. (t

CL,

t

CH)

min. (t

CL,

t

CH)

t

CK

Clock cycle time

CL = 3

5000

8000

5000

8000

ps

CL = 4 & 5

5000

8000

3750

8000

ps

t

IS

t

IH

t

DS

t

DH

t

IPW

t

DIPW

t

HZ

t

LZ(DQ)

t

LZ(DQS)

Address and control input setup time

600

-

600

-

ps

Address and control input hold time

600

-

600

-

ps

DQ and DM input setup time

400

-

350

-

ps

DQ and DM input hold time

400

-

350

-

ps

Control and Addr. input pulse width (each input)

0.6

-

0.6

-

t

CK

DQ and DM input pulse width (each input)

0.35

-

0.35

-

t

CK

Data-out high-impedance time from CK / CK

-

tACmax

-

tACmax

ps

DQ low-impedance from CK / CK

2*tACmin

tACmax

2*tACmin

tACmax

ps

DQS low-impedance from CK / CK

tACmin

tACmax

tACmin

tACmax

ps

t

DQSQ

DQS-DQ skew

(for DQS & associated DQ signals)

-

350

-

300

ps

t

QHS

t

QH

Data hold skew factor

-

450

-

400

ps

Data Output hold time from DQS

t

HP-tQHS

WL

-0.25

-

t

HP-tQHS

WL

-0.25

-

t

DQSS

Write command to 1st DQS latching transition

WL

+0.25

WL

+0.25

t

CK

t

DQSL,H

DQS input low (high) pulse width (write cycle)

0.35

-

0.35

-

t

CK

t

DSS

DQS falling edge to CLK setup time

(write cycle)

0.2

-

0.2

-

t

CK

t

DSH

DQS falling edge hold time from CLK

(write cycle)

0.2

-

0.2

-

t

CK

t

MRD

t

WPRE

t

WPST

t

RPRE

t

RPST

t

RAS

t

RC

t

RFC

Mode register set command cycle time

2

-

2

-

t

CK

Write preamble

0.25

-

0.25

-

t

CK

Write postamble

0.40

0.60

0.40

0.60

t

CK

Read preamble

0.9

1.1

0.9

1.1

t

CK

Read postamble

0.40

0.60

0.40

0.60

t

CK

Active to Precharge command

45

70000

45

70000

ns

Active to Active/Auto-refresh command period

60

-

60

-

ns

Auto-refresh to Active/Auto-refresh command period

105

-

105

-

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T64001GR | DDR2 Registered DIMM Modules |

| HYS72T64020GR-37-A | DDR2 Registered DIMM Modules |

| HYS72T32000GR-37-A | DDR2 Registered DIMM Modules |

| HYS72T64020GR-5-A | DDR2 Registered DIMM Modules |

| HYS72T32000GR-5-A | DDR2 Registered DIMM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T128000HR-5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T128001HR | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR SDRAM Modules |

| HYS72T128001HR-5-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR SDRAM Modules |

| HYS72T128020EU-2.5-B2 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T128020EU-25F-B2 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復。