- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370809 > HYS72T256220HR (INFINEON TECHNOLOGIES AG) DDR2 Registered Memory Modules PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72T256220HR |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | DDR2 Registered Memory Modules |

| 中文描述: | 注冊(cè)的DDR2內(nèi)存模塊 |

| 文件頁數(shù): | 7/33頁 |

| 文件大?。?/td> | 936K |

| 代理商: | HYS72T256220HR |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

HYS72T[256/128/64][0/2][0/2]0[G/H]R-[5/3.7]-A

Registered DDR2 SDRAM Modules

Data Sheet

Preliminary

7

Rev. 0.85, 2004-04

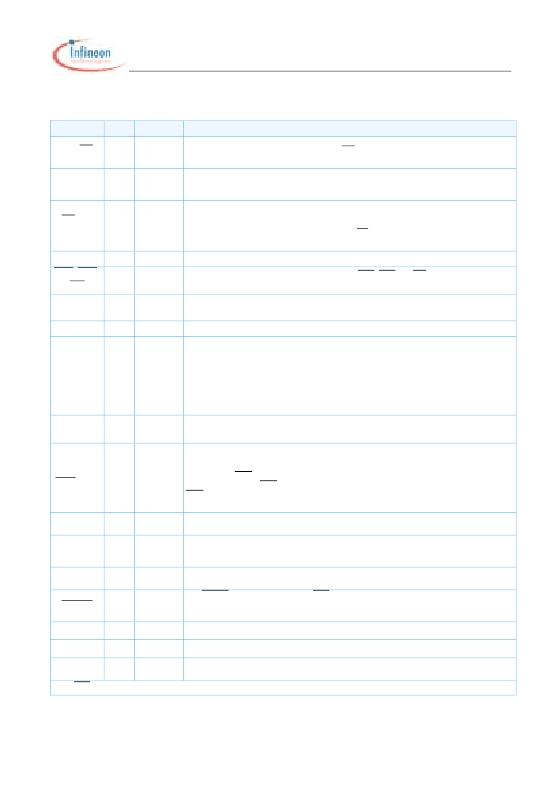

1.7 Registered DIMM Input/Output Functional Description

Symbol

Type

Polarity

Function

CK0, CK0

Input

Cross point

The system clock inputs. All address and command lines are sampled on the cross point of

the rising edge of CK and the falling edge of CK. An on-board DLL circuit is driven from the

clock inputs and output timing for read operations is synchronized to the input clock.

CKE[1:0]

Input

Active High

CKE high activates and CKE low deactivates internal clock signals and device input buffers

and output drivers of the SDRAMs. Taking CKE low provides Precharge Power-Down and

Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank).

CS[1:0]

Input

Active Low

Enables the associated SDRAM command decoder when low and disables decoder when

high. When decoder is disabled, new commands are ignored and previous operations con-

tinue. The input signals also disable all outputs (except CKE and ODT) of the register(s) on

the DIMM when both inputs are high. When both CS[1:0] are high, all register outputs (except

CK, ODT and Chip select) remain in the previous state.

ODT[1:0]

RAS, CAS,

WE

Input

Active High On-Die Termination control signals

Input

Active Low

When sampled at the positive edge of the clock, RAS, CAS and WE define the operation to

be executed by the SDRAM.

DM[8:0]

Input

Active High Masks write data when high, issued concurrently with input data.

BA[1:0]

Input

-

Selects which internal SDRAM memory bank is activated

A[13:0]

Input

-

During Bank Activate command cycle, Address defines the row address. During a Read or

Write command cycle, Address defines the column address. In addition to the column

address, A10(=AP) is used to invoke Auto-Precharge operation at the end of the burst read

or write cycle. If AP is high, Auto Precharge is selected and BA[1:0] defines the bank to be

precharged. If AP is low, Auto-Precharge is disabled. During a Precharge command cycle,

AP is used in conjunction with BA[1:0] to control which bank(s) to precharge. If AP is high, all

banks will be precharged regardless of the state of BA[1:0]. If AP is low, BA[1:0] are used to

define which bank to precharge.

DQ[63:0],

CB[7:0]

I/O

-

Data and Check Bit Input /Output pins.

DQS[17:0],

DQS[17:0]

I/O

Cross point

The data strobes, associated with one data byte, source with data transfer. In Write mode,

the data strobe is sourced by the controller and is centered in the data window. In Read

mode the data strobe is sources by the DDR2 SDRAM and is sent at the leading edge of the

data window. DQS signals are complements, and timing is relative to the crosspoint of

respective DQS and DQS. If the module is to be operated in single ended strobe mode, all

DQS signals must be tied on the system board to VSS and DDR2 SDRAM mode registers

programmed appropriately.

SA[2:0]

Input

-

These signals are tied at the system planar to either VSS or VDDSPD to configure the serial

SPD EEPROM address range

SDA

I/O

-

This bidirectional pin is used to transfer data into and out of the SPD EEPROM. A resistor

maybe connected from the SDA bus line to VDDSPD on the system planar to act as a pull-

up.

SCL

Input

-

This signal is used to clock data into the SPD EEPROM. A resistor maybe connected from

the SCL bus line to VDDSPD on the system planar to act as a pull-up.

RESET

Input

-

The RESET pin is connected to the RST pin on the register and to the OE pin on the PLL.

When low, all register outputs will be driven low and the PLL clocks to the DRAMs and the

register(s) will be set to low level. The PLL will remain synchronized with the input clock.

V

DD,

V

SS

Supply

-

Power and ground for the DDR SDRAM input buffers and core logic.

V

REF

Supply

-

Reference voltage for the SSTL-18 inputs.

V

DDSPD

Supply

-

Serial EEPROM positive power supply, wired to a separated power pin at the connector

which supports from 1.7 Volt to 3.6 Volt.

Note: CS1, ODT1 and CKE1 are used on dual rank modules only

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T512400AC-37 | M39012 MIL RF CONNECTOR |

| HYB18T512400AC-5 | M39012 MIL RF CONNECTOR |

| HYS72T256020HR-37-A | DDR2 Registered Memory Modules |

| HYS72T128000HR-37-A | DDR2 Registered Memory Modules |

| HYS72T256020HR-5-A | DDR2 Registered Memory Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T256220HR-3.7-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3.7-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3S-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3S-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。