- 您現(xiàn)在的位置:買賣IC網 > PDF目錄360699 > IBMB3N16644HCB-260 x64 SDRAM Module PDF資料下載

參數(shù)資料

| 型號: | IBMB3N16644HCB-260 |

| 英文描述: | x64 SDRAM Module |

| 中文描述: | X64的內存模塊 |

| 文件頁數(shù): | 7/20頁 |

| 文件大小: | 378K |

| 代理商: | IBMB3N16644HCB-260 |

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 7 of 20

IBM13N16644HCC

IBM13N16734HCC

16M x 64/72 Two-Bank Unbuffered SDRAM Module

19L7296.E93875B

12/99

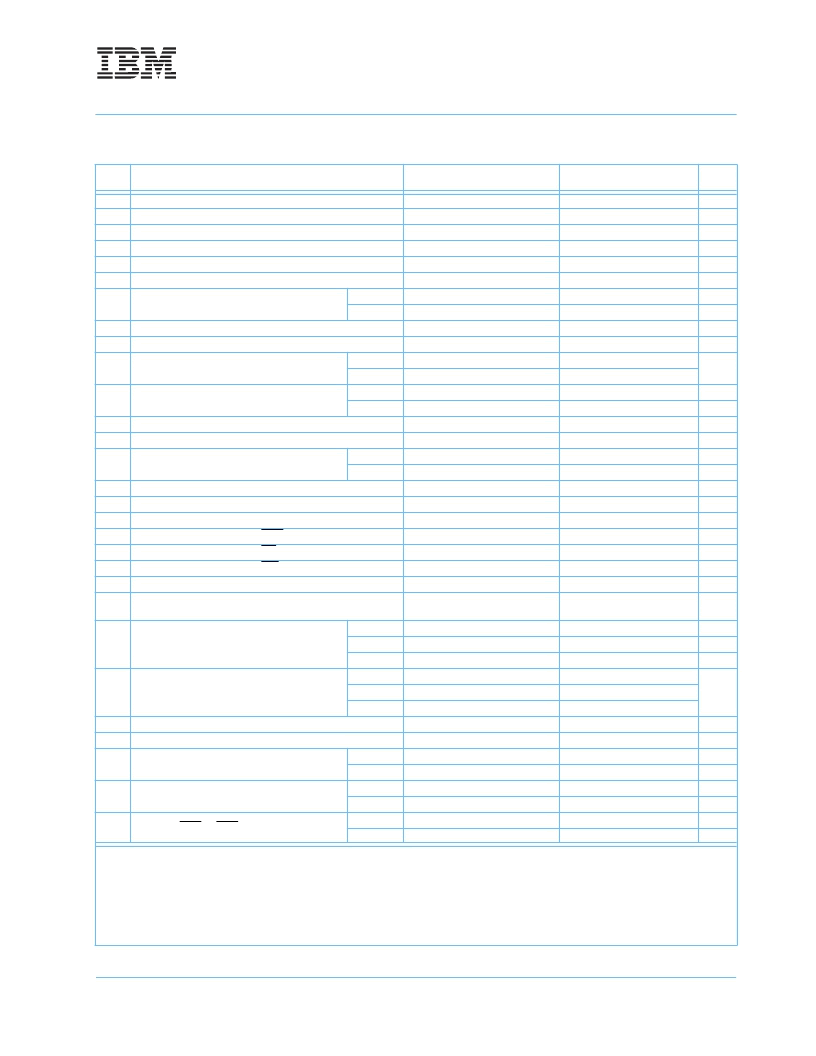

Serial Presence Detect (Part 1 of 3)

Byte #

Description

SPD Entry Value

Serial PD Data Entry

(Hexadecimal)

80

08

04

0C

09

02

4000

4800

01

A0

60

70

00

02

80

08

00

08

01

8F

04

06

01

01

00

Notes

0

1

2

3

4

5

Number of Serial PD Bytes Written during Production

Total Number of Bytes in Serial PD device

Fundamental Memory Type

Number of Row Addresses on Assembly

Number of Column Addresses on Assembly

Number of DIMM Banks

128

256

SDRAM

12

9

2

x64

x72

LVTTL

10.0ns

6.0ns

7.0ns

Non-Parity

ECC

SR/1x(15.625us)

x8

N/A

x8

1 Clock

1,2,4,8, Full Page

4

2, 3

0

0

Unbuffered

Wr-1/Rd Burst, Precharge All,

Auto-Precharge, V

DD

+/- 10%

10.0ns

15.0ns

15.0ns

6.0ns

9.0ns

8.0ns

N/A

N/A

20ns

30ns

20ns

20ns

20ns

30ns

6 - 7

Data Width of Assembly

16M x 64

16M x 72

8

9

Voltage Interface Level of this Assembly

SDRAM Device Cycle Time at CL=3

SDRAM Device Access Time from Clock

at CL=3

10

-260, -360

-10

16M x 64

16M x 72

1

11

DIMM Configuration Type

12

13

Refresh Rate/Type

Primary SDRAM Device Width

14

Error Checking SDRAM Device Width

16M x 64

16M x 72

15

16

17

18

19

20

21

SDRAM Device Attr: Min Clk Delay, Random Col Access

SDRAM Device Attributes: Burst Lengths Supported

SDRAM Device Attributes: Number of Device Banks

SDRAM Device Attributes: CAS Latencies Supported

SDRAM Device Attributes: CS Latency

SDRAM Device Attributes: WE Latency

SDRAM Module Attributes

22

SDRAM Device Attributes: General

0E

23

Minimum Clock Cycle at CL=2

-260

-360

-10

-260

-360

-10

A0

F0

F0

60

90

80

00

00

14

1E

14

14

14

1E

24

Maximum Data Access Time (t

AC

) from

Clock at CL=2

1

25

26

Minimum Clock Cycle Time at CL=1

Maximum Data Access Time (t

AC

) from Clock at CL=1

27

Minimum Row Precharge Time (t

RP

)

-260, -360

-10

-260, -360

-10

-260, -360

-10

28

Minimum Row Active to Row Active delay

(t

RRD

)

29

Minimum RAS to CAS delay (t

RCD

)

1. See the AC output load circuit in the AC Characteristics section below

2. cc = Checksum Data byte, 00-FF (Hex)

3. “R” = Alphanumeric revision code, A-Z, 0-9

4. rr = ASCII coded revision code byte “R”

5. yy = Binary coded decimal year code, 00-99 (Decimal)

00-63 (Hex)

6. ww = Binary coded decimal week code, 01-52 (Decimal)

01-34 (Hex)

7. ss = Serial number data byte, 00-FF (Hex)

相關PDF資料 |

PDF描述 |

|---|---|

| IBMB3N16644HCB-360 | x64 SDRAM Module |

| IBMB3N16644HCB-75AT | x64 SDRAM Module |

| IBMB3N16734HCB-260 | x72 SDRAM Module |

| IBMB3N16734HCB-360 | x72 SDRAM Module |

| IBMB3N16734HCB-75AT | x72 SDRAM Module |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IBMFDM44H-064J | 制造商:STEC Inc 功能描述:64MB FLASH 44PIN HORIZ IBM - Bulk |

| IBMFDM44H-064J-01 | 制造商:STEC Inc 功能描述:AKA:IBM00-01234-0A1C - Bulk |

| IBMFDM44H-064JU-01 | 制造商:STEC Inc 功能描述:AKA: IBM00-01234-0B1CU - Bulk |

| IBMFDM44H-128MM1U | 制造商:STEC Inc 功能描述:128MB CF, COMMERCIAL TEMP - Bulk |

| IBMN364164CT3C360 | 制造商:IBM 功能描述:* |

發(fā)布緊急采購,3分鐘左右您將得到回復。