- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383083 > ICL8052CPD (INTERSIL CORP) 14-Bit/16-Bit, Microprocessor- Compatible, 2-Chip, A/D Converter PDF資料下載

參數(shù)資料

| 型號: | ICL8052CPD |

| 廠商: | INTERSIL CORP |

| 元件分類: | 模擬信號調理 |

| 英文描述: | 14-Bit/16-Bit, Microprocessor- Compatible, 2-Chip, A/D Converter |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PDIP14 |

| 封裝: | PLASTIC, DIP-14 |

| 文件頁數(shù): | 15/21頁 |

| 文件大?。?/td> | 198K |

| 代理商: | ICL8052CPD |

5-20

Detailed Description

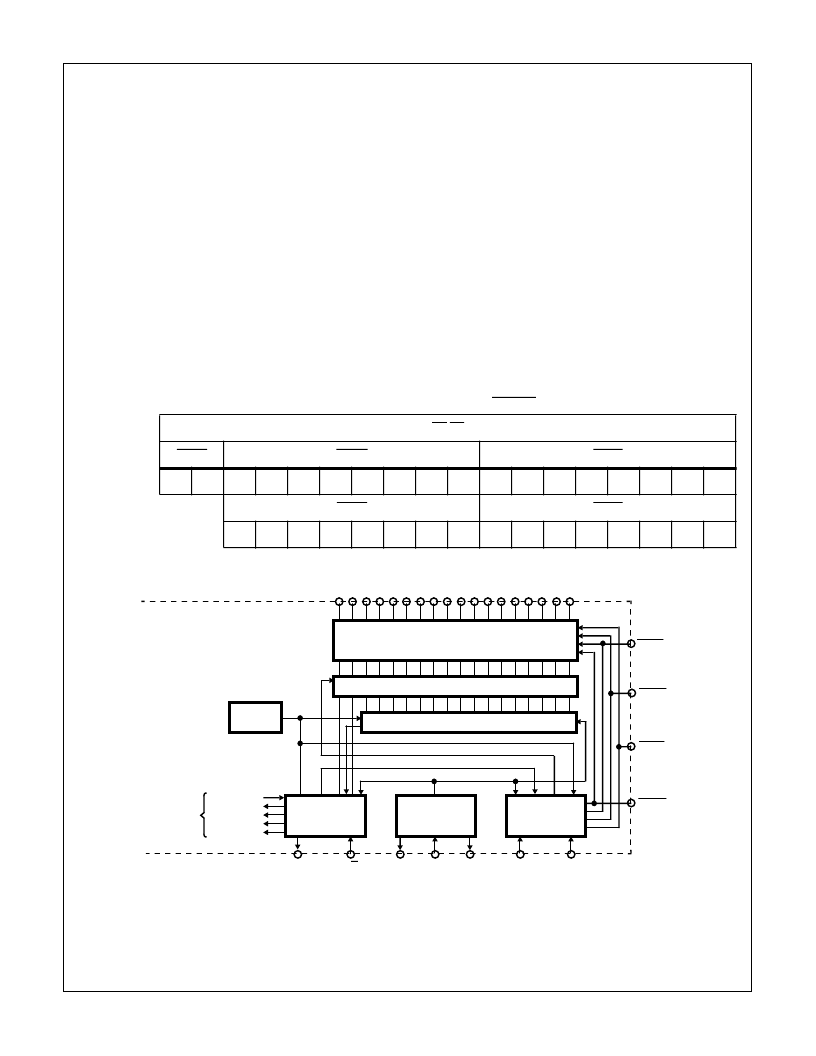

DIGITAL SECTION

The digital section includes the clock oscillator circuit, a

16-bit or 14-bit binary counter with output latches and TTL-

compatible three-state output drivers, polarity, over-range

and control logic and UART handshake logic, as shown in

the Block Diagram Figure 9 (16-bit version shown).

Throughout this description, logic levels will be referred to as

“l(fā)ow” or “high”. The actual logic levels are defined under

“ICL7104 Electrical Specification”. For minimum power con-

sumption, all inputs should swing from GND (low) to V+

(high). Inputs driven from TTL gates should have 3 - 5k

pullup resistors added for maximum noise immunity.

MODE Input

The MODE input is used to control the output mode of the

converter. When the MODE pin is connected to GND or left

open (this input is provided with a pulldown resistor to

ensure a low level when the pin is left open), the converter is

in its “Direct” output mode, where the output data is directly

accessible under the control of the chip and byte enable

inputs. When the MODE input is pulsed high, the converter

enters the UART handshake mode and outputs the data in

three bytes for the 7104-16 or two bytes for the 7104-14 then

returns to “direct” mode. When the MODE input is left high,

the converter will output data in the handshake mode at the

end of every conversion cycle. (See section entitled “Hand-

shake Mode” for further details).

STATUS Output

During a conversion cycle, the STATUS output goes high at

the beginning of Input Integrate (Phase II), and goes low

one-half clock period after new data from the conversion has

been stored in the output latches. See Figure 8 for details of

this timing. This signal may be used as a “data valid” flag

(data never changes while STATUS is low) to drive inter-

rupts, or for monitoring the status of the converter.

TABLE 5. THREE-STATE BYTE FORMATS AND ENABLE PINS

CE/LD

HBEN

MBEN

LBEN

ICL7104-16

POL

O/R

B16

B15

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

HBEN

LBEN

ICL7104-14

POL

O/R

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

FIGURE 9. DIGITAL SECTION

HBEN

MBEN

(-16 ONLY)

LBEN

CE/LD

OSCILLATOR

AND CLOCK

CIRCUITRY

27

SEND

21

MODE

25

CLOCK

(3)

23

CLOCK

(2)

24

2

STATUS

26

R/H

18/16 THREE-STATE OUTPUTS

18/16 LATCHES

18/16 BIT COUNTER

LATCH

CLOCK

HANDSHAKE

LOGIC

CONVERSION

CONTROL

LOGIC

INITIAL

CLEAR

CLOCK

(1)

COMP OUT

AZ

INT

DEINT(+)

DEINT(-)

TO

ANALOG

SECTION

ICL8052/ICL7104, ICL8068/ICL7104

相關PDF資料 |

PDF描述 |

|---|---|

| ICL7104-16 | 16-Bit, Microprocessor-Compatible, 2-Chip, A/D Converter(16位、微處理器兼容的2片ADC) |

| ICL7104 | 14-Bit/16-Bit, Microprocessor- Compatible, 2-Chip, A/D Converter |

| ICL7104-14CPL | 14-Bit/16-Bit, Microprocessor- Compatible, 2-Chip, A/D Converter |

| ICL7104-16CPL | 14-Bit/16-Bit, Microprocessor- Compatible, 2-Chip, A/D Converter |

| ICL7106 | 3 1/2 Digital ADC(3 1/2位數(shù),具有直接液晶顯示驅動器的ADC) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ICL8052CPL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| ICL8053 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Precision Chip Pairs for A/D Conversion |

| ICL8053A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Precision Chip Pairs for A/D Conversion |

| ICL8053ACDD | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Precision Chip Pairs for A/D Conversion |

| ICL8053ACPD | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Precision Chip Pairs for A/D Conversion |

發(fā)布緊急采購,3分鐘左右您將得到回復。