- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360778 > ICS9148F-02 Pentium/ProTM System Clock Chip PDF資料下載

參數(shù)資料

| 型號(hào): | ICS9148F-02 |

| 英文描述: | Pentium/ProTM System Clock Chip |

| 中文描述: | 奔騰/ ProTM系統(tǒng)時(shí)鐘芯片 |

| 文件頁(yè)數(shù): | 6/16頁(yè) |

| 文件大小: | 691K |

| 代理商: | ICS9148F-02 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

6

ICS9148-02

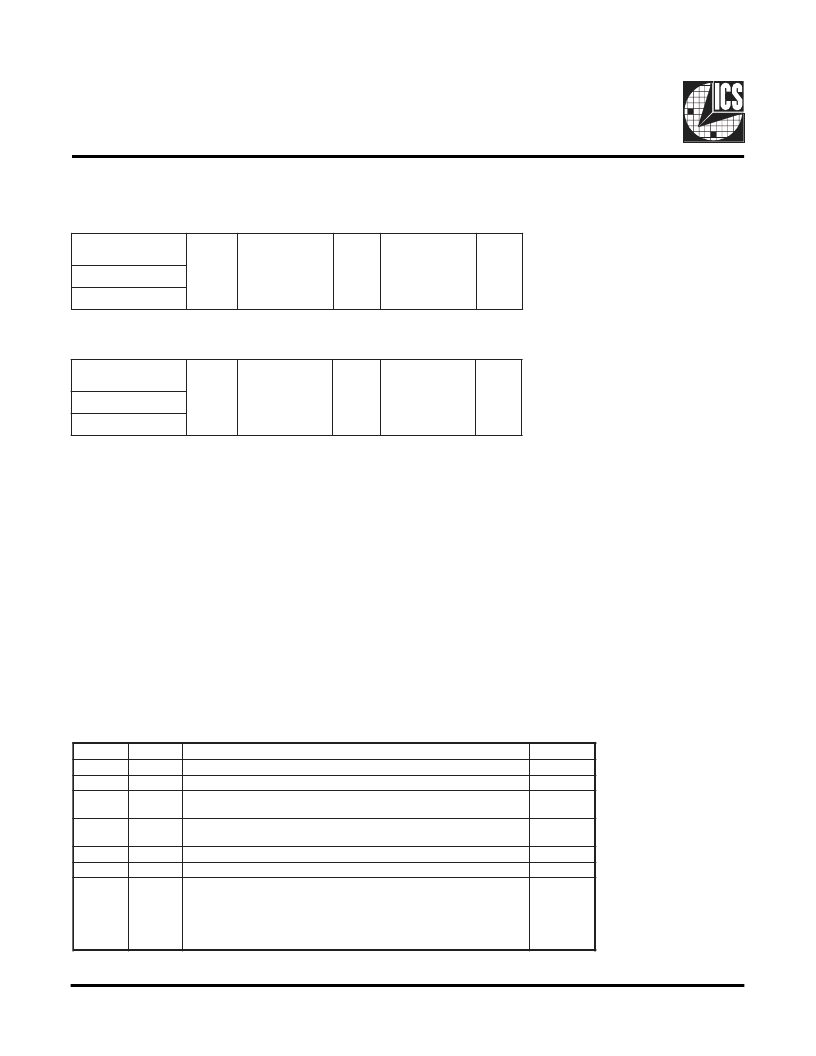

Serial Configuration Command Bitmaps

Byte 0: Functional and Frequency Select Clock Register (default on Bits 7, 6, 5, 4, 1, 0 = 0)

Note:

PWD = Power-Up Default

(default on Bits 3, 2 = 1)

General I

2

C serial interface information

A.

For the clock generator to be addressed by an I

2

C controller, the following address must be sent as a start sequence, with

an acknowledge bit between each byte.

r

n

e

G

k

)

7

s

d

K

C

A

e

d

c

d

n

a

m

m

o

c

e

B

#

W

/

R

&

)

A

B.

The clock generator is a slave/receiver I

2

C component. It can "read back "(in Philips I

2

C protocol) the data stored in the

latches for verification. (set R/W# to 1 above). There is no BYTE count supported, so it does not meet the Intel SMB

PIIX4 protocol.

C.

The data transfer rate supported by this clock generator is 100K bits/sec (standard mode)

D.

The input is operating at 3.3V logic levels.

E.

The data byte format is 8 bit bytes.

To simplify the clock generator I

2

C interface, the protocol is set to use only block writes from the controller. The bytes

must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has

been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those two

bytes. The data is loaded until a Stop sequence is issued.

F.

G

In the power down mode (PWR_DWN# Low), the SDATA and SCLK pins are tristated and the internal data latches

maintain all prior programming information.

H.

At power-on, all registers are set to a default condition. See Byte 0 detail for default condition, Bytes 1 through 5 default

to a 1 (Enabled output state)

Then Byte 0, 1, 2, etc in

sequence until STOP.

Byte 0, 1, 2, etc in sequence until STOP.

I

2

C is a trademark of

Philips Corporation

T

I

B

t

B

t

B

#

N

-

-

I

P

N

O

I

T

P

I

R

C

S

E

D

D

W

0

0

P

7

6

d

e

e

a

v

R

t

u

M

S

n

=

0

S

n

8

=

0

2

4

2

4

n

y

o

p

s

o

a

e

s

s

o

o

l

,

n

w

,

m

m

m

o

r

n

u

e

=

1

u

p

%

6

=

e

F

(

z

H

F

(

z

H

B

1

0

1

0

r

p

S

,

S

1

0

d

b

5

t

B

-

e

p

C

e

e

e

c

a

%

M

4

M

4

1

B

1

1

0

0

)

d

0

4

t

B

g

n

a

S

C

d

)

q

q

0

3

2

t

t

B

B

3

2

2

2

z

z

H

H

M

M

4

4

2

2

=

=

0

0

,

,

H

H

M

M

8

8

4

4

=

=

1

1

)

)

e

S

e

S

y

y

c

c

n

n

e

e

u

u

1

1

e

0

-

-

-

-

1

0

t

t

B

B

-

e

-

T

e

S

m

t

T

m

r

N

e

a

n

E

m

u

e

p

S

e

d

d

o

l

a

n

o

p

o

0

0

c

o

C

A

y

m

m

u

d

s

8

+

K

C

A

y

m

m

t

u

u

d

o

c

s

8

+

K

C

A

2

D

)

H

(

r

n

)

7

e

G

k

c

o

C

A

s

d

K

C

A

0

e

B

K

C

A

1

e

B

K

C

A

#

W

/

R

&

)

A

3

D

)

H

(

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS9148F-03 | Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148F-11 | Frequency Generator & Integrated Buffers for PENTIUMTM |

| ICS9148F-13 | Frequency Generator & Integrated Buffers for PENTIUMTM |

| ICS9148F-18 | VARISTOR BLOCK 275VRMS 32MM |

| ICS9148F-20 | VARISTOR BLOCK 550VRMS 32MM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS9148F-02CW | 制造商:ICS 功能描述:9148F-02CW |

| ICS9148F-02T | 制造商:ICS 功能描述:9148F-02T |

| ICS9148F-03 | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148F05 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Interface IC |

| ICS9148F06 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Interface IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。