- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360782 > ICS9248-168 18-Bit Buffers/Drivers With 3-State Outputs 56-SSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | ICS9248-168 |

| 英文描述: | 18-Bit Buffers/Drivers With 3-State Outputs 56-SSOP -40 to 85 |

| 中文描述: | AMD公司- k7的⑩時(shí)鐘發(fā)生器移動(dòng)通信系統(tǒng) |

| 文件頁(yè)數(shù): | 8/11頁(yè) |

| 文件大?。?/td> | 100K |

| 代理商: | ICS9248-168 |

8

ICS9248-185

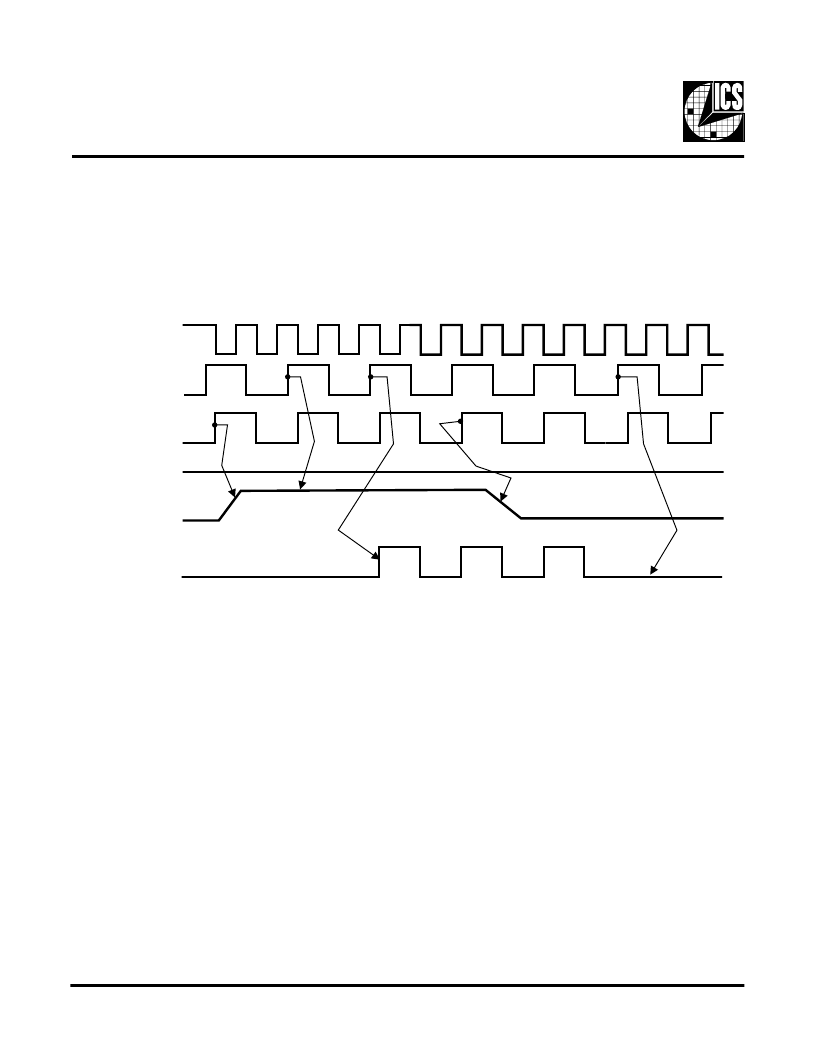

PCI_STOP# Timing Diagram

PCI_STOP# is an asynchronous input to the

ICS9248-185

. It is used to turn off the PCICLK clocks for low power operation.

PCI_STOP# is synchronized by the

ICS9248-185

internally. The minimum that the PCICLK clocks are enabled (PCI_STOP#

high pulse) is at least 10 PCICLK clocks. PCICLK clocks are stopped in a low state and started with a full high pulse width

guaranteed. PCICLK clock on latency cycles are only three rising PCICLK clocks, off latency is one PCICLK clock.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248 device.)

2. PCI_STOP# is an asynchronous input, and metastable conditions may exist. This signal is required to be synchronized

inside the ICS9248.

3. All other clocks continue to run undisturbed.

4. CLK_STOP# is shown in a high (true) state.

CPUCLK

(Internal)

PCICLK_F

(Internal)

PCICLK_F

(Free-running)

CLK_STOP#

PCICLK [6:0]

PCI_STOP#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS9248-20 | Pentium/ProTM System Clock Chip |

| ICS9248-39 | Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9248-55 | Pentium/Pro/IITM System Clock Chip |

| ICS9248-56 | 20-Bit Buffers/Drivers With 3-State Outputs 56-TSSOP -40 to 85 |

| ICS9248-61 | Frequency Timing Generator for Pentium II Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS9248-171 | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7TM System Clock Chip |

| ICS9248-185 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM & K6 |

| ICS9248-189 | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7⑩ Clock Generator for Mobile System |

| ICS9248-192 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Timing Generator for Transmeta Systems |

| ICS9248-195 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM II/III & K6 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。