- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377248 > IDT6168SA35SO (INTEGRATED DEVICE TECHNOLOGY INC) CMOS STATIC RAM 16K (4K x 4-BIT) PDF資料下載

參數(shù)資料

| 型號(hào): | IDT6168SA35SO |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS STATIC RAM 16K (4K x 4-BIT) |

| 中文描述: | 4K X 4 STANDARD SRAM, 35 ns, PDSO20 |

| 封裝: | 0.300 INCH, 1.27 MM PITCH, SOIC-20 |

| 文件頁數(shù): | 7/9頁 |

| 文件大小: | 91K |

| 代理商: | IDT6168SA35SO |

6.42

IDT6168SA/LA

CMOS Static RAM 16K (4K x 4-Bit) Military, Industrial, and Commercial Temperature Ranges

7

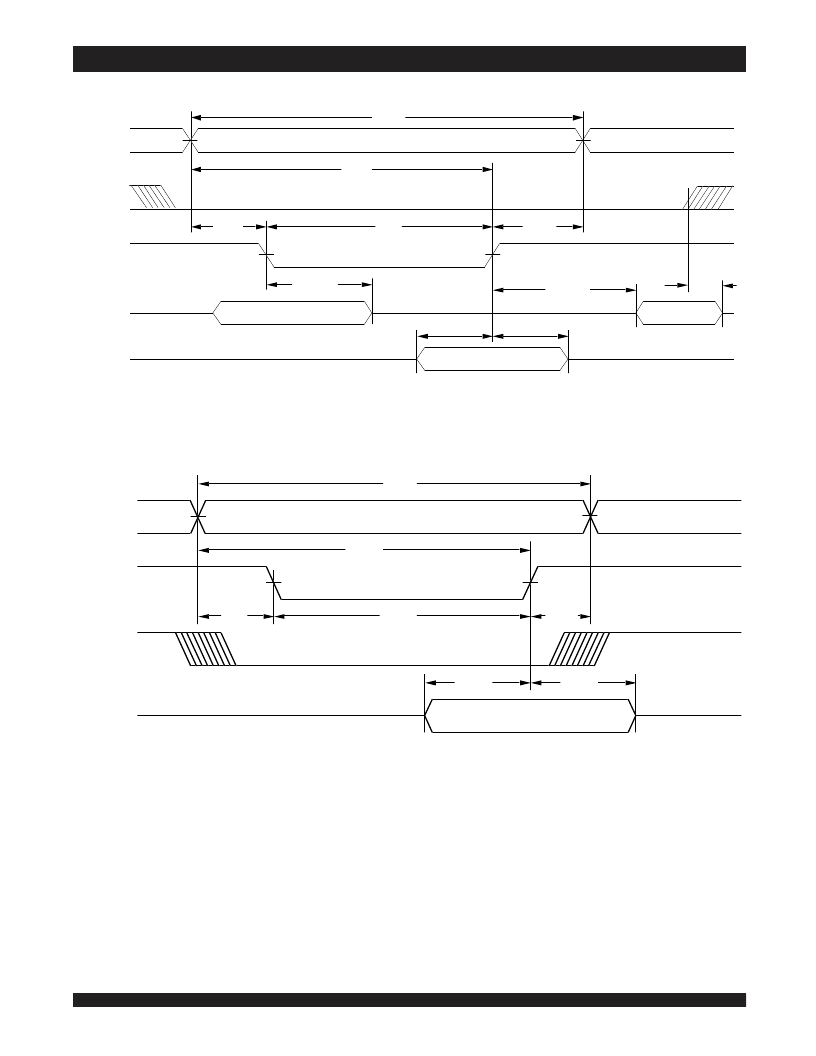

Timing Waveform of Write Cycle No. 2 (

CS

Controlled Timing)

(1,2,5)

NOTES:

1.

WE

or

CS

must be HIGH during all address transitions.

2. A write occurs during the overlap of a LOW

CS

and a LOW

WE

.

3. t

WR

is measured fromthe earlier of

CS

or

WE

going HIGH to the end of the write cycle.

4. During this period, the I/O pins are in the output state and input signals should not be applied.

5. If the

CS

LOW transition occurs simultaneously with or after the

WE

LOW transition, the outputs remain in the high impedance state.

6. Transition is measured ±200mV fromsteady state.

Timing Waveform of Write Cycle No. 1 (

WE

Controlled Timing)

(1,2,5)

CS

DATA

IN

ADDRESS

WE

DATA

OUT

3090 drw 08

t

AW

t

WR

t

DW

t

WC

t

WP

t

DH

t

WHZ

t

OW

(4)

t

AS

(6)

(4)

(6)

DATA VALID

PREVIOUS DATA VALID

DATA

VALID

(3)

t

CHZ

(6)

,

WR

t

CS

3090 drw 09

t

AW

t

DW

DATA

IN

ADDRESS

t

WC

WE

t

CW

t

DH

AS

t

DATA VALID

(3)

,

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT6168SA45D | Low-Power JFET-Input Operational Amplifier 8-PDIP 0 to 70 |

| IDT6168SA45LB | Low-Power JFET-Input Operational Amplifier 8-SO 0 to 70 |

| IDT6168SA45P | Low-Power JFET-Input Operational Amplifier 8-SO 0 to 70 |

| IDT6168SA25PB | CMOS STATIC RAM 16K (4K x 4-BIT) |

| IDT6168LA25PB | CMOS STATIC RAM 16K (4K x 4-BIT) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT6168SA35SOB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (4K x 4-BIT) |

| IDT6168SA35Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SRAM |

| IDT6168SA45D | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (4K x 4-BIT) |

| IDT6168SA45DB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (4K x 4-BIT) |

| IDT6168SA45EB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。