- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377249 > IDT6178S10PB (Integrated Device Technology, Inc.) CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM PDF資料下載

參數(shù)資料

| 型號(hào): | IDT6178S10PB |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

| 中文描述: | 的CMOS StaticRAM 16K的(4K的× 4位)高速緩存標(biāo)記內(nèi)存 |

| 文件頁(yè)數(shù): | 4/7頁(yè) |

| 文件大?。?/td> | 72K |

| 代理商: | IDT6178S10PB |

11.1

4

IDT6178S

CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGE

CYCLE DESCRIPTION

Match Cycle:

A match cycle occurs when all control signals

(

OE

,

WE

,

CLR

) are HIGH. At that time, data supplied to the

RAM on the I/O pins is compared with the data stored at the

specified address. The totem-pole match output is HIGH

when there is a match at all data bits, and drives LOW if there

is not a match.

Write Cycle:

The write cycle is conventional, occuring when

WE

is LOW and

CLR

is HIGH.

OE

may be either HIGH or LOW,

since it is overridden by

WE

. The state of the Match pin is not

guaranteed, but in the current implementation it continues to

reflect the output of the comparator. The Match pin goes

HIGH during write cycles since the data at the specified

address is the same as the data (being written) at the I/Os of

the RAM.

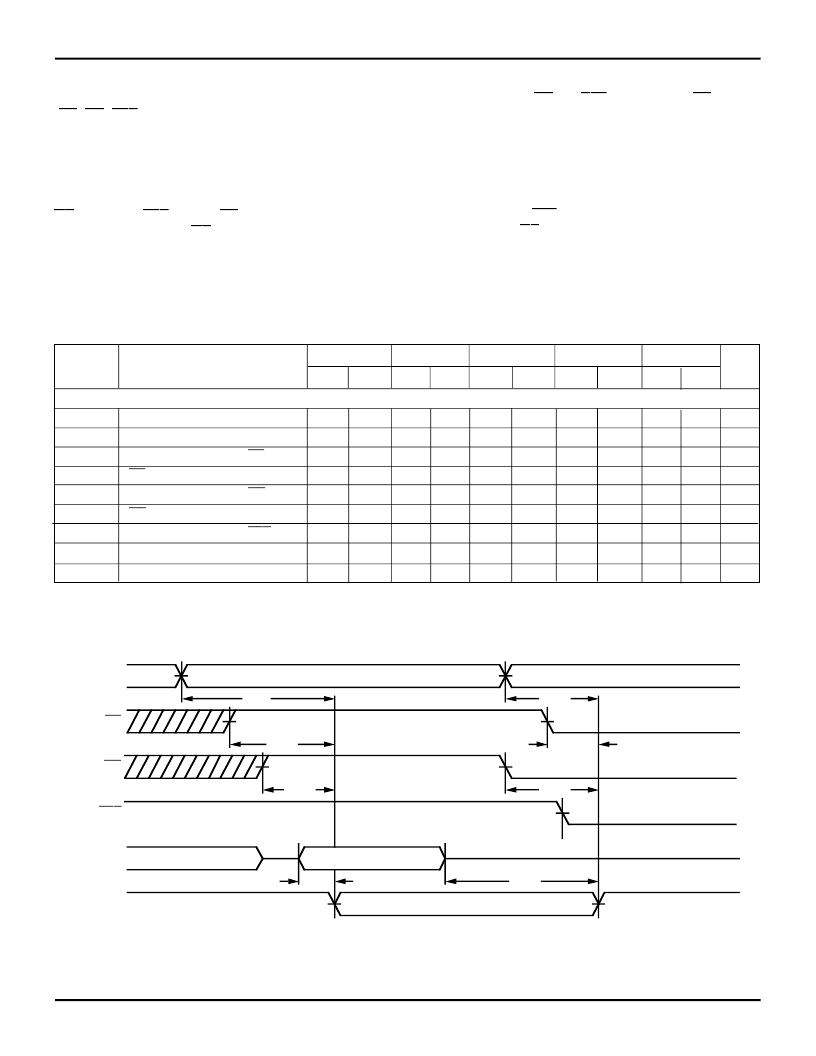

AC ELECTRICAL CHARACTERISTICS

(V

CC

= 5.0V

±

10%, All Temperature Ranges)

Read Cycle:

When

WE

and

CLR

are HIGH and

OE

is LOW,

the RAM is in a read cycle. The state of the Match pin is not

guaranteed, but in the current implementation it continues to

reflect the output of the comparator. The Match pin goes

HIGH during read cycles since the data at the specified

address is the same as the data (being read) at the I/Os of the

RAM.

Clear Cycle:

When

CLR

is asserted, every bit in the RAM is

cleared to zero. If

OE

is LOW during a clear cycle, the RAM

I/Os will be driven. However, this data is not necessarily

zeros, even after a considerable time. The Match pin is

enabled, but its state is not predicable.

NOTE:

1. It is not recommended to let address and data input pins float while MATCH pin is active.

TIMING WAVEFORM OF MATCH CYCLE

(1)

6178S10

(1)

6178S12

6178S15

6178S20

6178S25

Symbol

Match Cycle

t

ADM

t

DAM

t

MHO

t

OEM

t

MHW

t

WEM

t

MHCLR

t

MHA

t

MHD

Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Unit

Address to Match Valid

Data Input to Match Valid

Match Valid Hold from

OE

OE

HIGH to Match Valid

Match Valid Hold from

WE

WE

HIGH to Match Valid

Match Valid Hold from

CLR

Match Valid Hold from Address

Match Valid Hold from Data

—

—

0

—

0

—

0

3

3

10

8

—

10

—

10

—

—

—

—

—

0

—

0

—

0

3

3

12

11

—

12

—

12

—

—

—

—

—

0

—

0

—

0

3

3

15

13

—

15

—

15

—

—

—

—

—

0

—

0

—

0

3

3

20

15

—

20

—

20

—

—

—

—

—

0

—

0

—

0

3

3

25

15

—

20

—

20

—

—

—

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTE:

1. 0

°

C to +70

°

C temperature range only.

2953 tbl 10

2953 drw 07

OE

ADDRESS

t

MHA

t

ADM

t

OEM

t

MHO

WE

CLR

I/O

1–4

MATCH

t

WEM

t

MHW

t

MHCLR

t

MHD

t

DAM

VALID MATCH DATA

IN

MATCH VALID

MATCH

MATCH

NO MATCH

VALID READ DATA

OUT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT6178S10Y | IC 16-BIT 2 PORT BUS SW 48-BQSOP |

| IDT6178S10YB | 3.3V 24:48 Mux/Demux Bus Switch |

| IDT6178S25D | IC 8-BIT BUS SW 2-PORT 20-QSOP |

| IDT6178S25DB | CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

| IDT6178S25P | 3.3V, 8 BIT BUS SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT6178S10Y | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

| IDT6178S10YB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

| IDT6178S12CB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 Cache-Tag RAM |

| IDT6178S12D | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

| IDT6178S12DB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:CMOS StaticRAM 16K (4K x 4-BIT) CACHE-TAG RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。