- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377306 > IDT7132LA35JB (INTEGRATED DEVICE TECHNOLOGY INC) HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | IDT7132LA35JB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

| 中文描述: | 2K X 8 DUAL-PORT SRAM, 35 ns, PQCC52 |

| 封裝: | 0.750 X 0.750 INCH, 0.170 INCH HEIGHT, PLASTIC, LCC-52 |

| 文件頁(yè)數(shù): | 11/11頁(yè) |

| 文件大?。?/td> | 175K |

| 代理商: | IDT7132LA35JB |

6.02

11

IDT7132SA/LA AND IDT7142SA/LA

HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

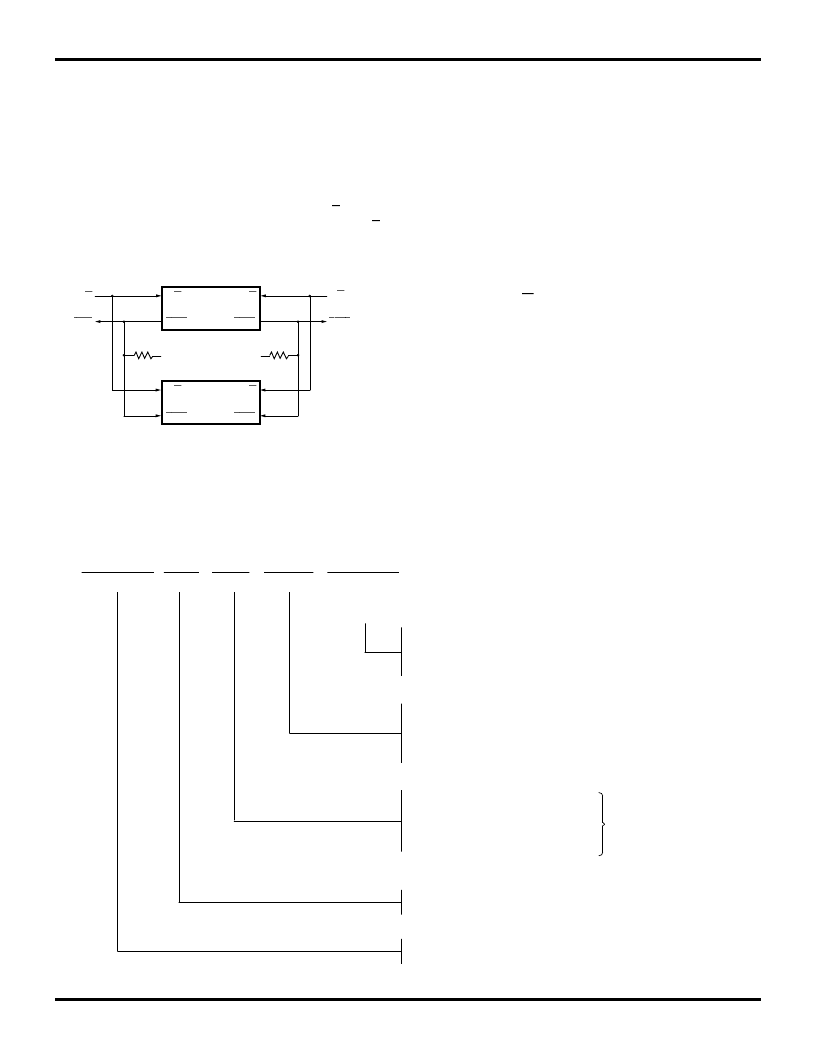

WIDTH EXPANSION WITH BUSY LOGIC

MASTER/SLAVE ARRAYS

When expanding an RAM array in width while using busy

logic, one master part is used to decide which side of the RAM

array will receive a busy indication, and to output that indica-

tion. Any number of slaves to be addressed in the same

address range as the master, use the busy signal as a write

inhibit signal. Thus on the IDT7130/IDT7140 RAM the busy

pin is an output if the part is used as a master (M/

S

pin = V

IH

),

and the busy pin is an input if the part used as a slave (M/

S

pin

= V

IL

) as shown in Figure 4.

Figure 4. Busy and chip enable routing for both width and depth

expansion with IDT7132 (Master) and IDT7142 (Slave) RAMs.

+5V

R/

W

BUSY

R/

W

BUSY

IDT7132

+5V

R/

W

BUSY

R/

W

BUSY

R/

W

BUSY

R/

W

BUSY

(1)

LEFT

RIGHT

2692 drw 15

ISLAVE

270

270

If two or more master parts were used when expanding in

width, a split decision could result with one master indicating

busy on one side of the array and another master indicating

busy on one other side of the array. This would inhibit the write

operations from one port for part of a word and inhibit the write

operations from the other port for the other part of the word.

The busy arbitration, on a master, is based on the chip enable

and address signals only. It ignores whether an access is a

read or write. In a master/slave array, both address and chip

enable must be valid long enough for a busy flag to be output

from the master before the actual write pulse can be initiated

with either the R/

W

signal or the byte enables. Failure to

observe this timing can result in a glitched internal write inhibit

signal and corrupted data in the slave.

48-pin Plastic DIP (P48-1)

48-pin Sidebraze DIP (C48-2)

52-pin PLCC (J52-1)

48-pin LCC (L48-1)

48-pin Ceramic Flatpack (F48-1)

XXXX

IDT

Device Type

A

999

Speed

A

A

Power

Package

Process/

Temperature

Range

7132

7142

Speed in nanoseconds

16K (2K x 8-Bit) MASTER Dual-Port RAM

16K (2K x 8-Bit) SLAVE Dual-Port RAM

Commercial PLCC Only

2692 drw 16

Blank

B

P

C

J

L48

F

20

25

35

55

100

LA

SA

Commercial (0

°

C to +70

°

C)

Military (–55

°

C to +125

°

C)

Compliant to MIL-STD-883, Class B

Low Power

Standard Power

ORDERING INFORMATION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7132LA35L48 | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

| IDT7132LA35L48B | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

| IDT7132LA35P | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

| IDT7132LA35PB | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

| IDT7132LA55C | HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7132LA35L48B | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 16KBIT 35NS 48LCC |

| IDT7132LA35P | 功能描述:IC SRAM 16KBIT 35NS 48DIP RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:72 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 同步 存儲(chǔ)容量:9M(256K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:71V67703S75PFGI |

| IDT7132LA35PDG | 功能描述:IC SRAM 16KBIT 35NS 48DIP RoHS:是 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:72 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 同步 存儲(chǔ)容量:9M(256K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:71V67703S75PFGI |

| IDT7132LA55C | 功能描述:IC SRAM 16KBIT 55NS 48DIP RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 雙端口,同步 存儲(chǔ)容量:1.125M(32K x 36) 速度:5ns 接口:并聯(lián) 電源電壓:3.15 V ~ 3.45 V 工作溫度:-40°C ~ 85°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-CABGA(17x17) 包裝:帶卷 (TR) 其它名稱:70V3579S5BCI8 |

| IDT7132LA55CB | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 16KBIT 55NS SB48 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。