- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377362 > IDT7202LA80SOB (INTEGRATED DEVICE TECHNOLOGY INC) CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 PDF資料下載

參數(shù)資料

| 型號: | IDT7202LA80SOB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| 中文描述: | 1K X 9 OTHER FIFO, 80 ns, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁數(shù): | 2/14頁 |

| 文件大?。?/td> | 153K |

| 代理商: | IDT7202LA80SOB |

5.09

2

MILITARY AND COMMERCIAL TEMPERATURE RANGES

IDT72021, IDT72031, IDT72041

CMOS ASYNCHRONOUS FIFO WITH RETRANSMIT 1K x 9, 2K x 9, 4K x 9

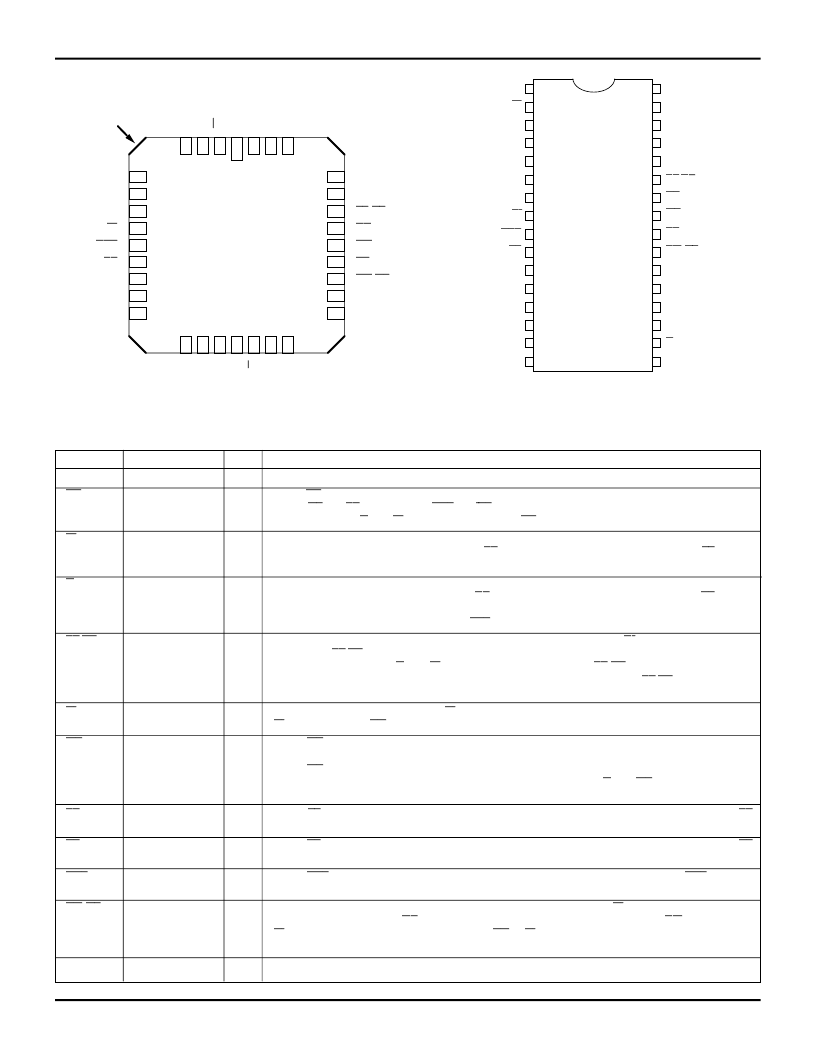

PIN CONFIGURATIONS

PIN DESCRIPTIONS

Symbol

D

0

–D

8

RS

Name

Inputs

Reset

I/O

I

I

Description

Data inputs for 9-bit wide data.

When

RS

is set LOW, internal READ and WRITE pointers are set to the first location of the RAM

array.

HF

and

FF

go HIGH, and

AEF

and

EF

go LOW. A reset is required before an initial WRITE

after power-up.

R

and

W

must be HIGH during

RS

cycle.

When WRITE is LOW, data can be written into the RAM array sequentially, independent of

READ. In order for WRITE to be active,

FF

must be HIGH. When the FIFO is full (

FF

-LOW),

the internal WRITE operation is blocked.

When READ is LOW, data can be read from the RAM array sequentially, independent of

WRITE. In order for READ to be active,

EF

must be HIGH. When the FIFO is empty (

EF

-LOW),

the internal READ operation is blocked. The three-state output buffer is controlled by the read

signal and the external output control

(OE

).

This is a dual-purpose input. In the single device configuration (

XI

grounded), activating

retransmit (

FL

/

RT

-LOW) will set the internal READ pointer to the first location. There is no effect

on the WRITE pointer.

R

and

W

must be HIGH before setting

FL

/

RT

LOW. Retransmit is not

compatible with depth expansion. In the depth expansion configuration,

FL

/

RT

-LOW indicates

the first activated device.

In the single device configuration,

XI

is grounded. In depth expansion or daisy chain expansion,

XI

is connected to

XO

(expansion out) of the previous device.

When

OE

is set HIGH, the data flow through the three-state output buffer is inhibited regardless

of an active READ operation. A read operation does increment the read pointer in this situation.

When

OE

is set LOW, Q

0

-Q

8

are still in a HIGH impedance condition if no READ occurs. For

a complete READ operation with data appearing on Q

0

-Q

8

, both

R

and

OE

should be asserted

LOW.

When

FF

goes LOW, the device is full and further WRITE operations are inhibited. When

FF

is HIGH, the device is not full.

When

EF

goes LOW, the device is empty and further READ operations are inhibited. When

EF

is HIGH, the device is not empty.

When

AEF

is LOW, the device is empty to 1/8 full or 7/8 to completely full. When

AEF

is HIGH,

the device is greater than 1/8 full, but less than 7/8 full.

This is a dual purpose output. In the single device configuration (

XI

grounded), the device is

more than half full when

HF

is LOW. In the depth expansion configuration (

XO

connected to

XI

of the next device), a pulse is sent from

XO

to

XI

when the last location in the RAM array is

filled.

Data outputs for 9-bit wide data.

W

Write

I

R

Read

I

FL

/

RT

First Load/

I

XI

Expansion In

I

OE

Output Enable

I

FF

Full Flag

O

EF

Empty Flag

O

AEF

Almost-Empty/

Almost-Full Flag

O

XO

/

HF

Expansion Out/

Half-Full Flag

O

Q

0

–Q

8

Outputs

O

Retransmit

2677 tbl 01

PLCC TOP VIEW

DIP TOP VIEW

D

2

D

1

D

0

XI

5

6

7

8

9

10

11

12

13

AEF

FF

Q

0

Q

1

Q

2

D

6

D

7

FL

/

RT

RS

OE

EF

XO

/

HF

Q

7

Q

6

29

28

27

26

25

24

23

22

21

4

3

2

132 31 30

14 15 16 17 18 19 20

Q

3

Q

8

G

G

R

Q

4

Q

5

D

3

D

8

W

V

C

V

C

D

4

D

5

INDEX

J32-1

2677 drw 03

V

CC

D

4

D

5

D

6

D

7

FL

/

RT

RS

OE

XO

/

HF

EF

Q

7

Q

6

Q

5

Q

4

R

GND

V

CC

W

D

8

D

3

D

2

D

1

D

0

XI

AEF

FF

Q

0

Q

1

Q

2

Q

3

Q

8

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

D32-1

2677 drw 02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7202LA80TD | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7202LA80TDB | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7202LA80TP | RAC10-SB(-E)(-ST) Series - Powerline Regulated AC-DC Converters; Output Voltage (Vdc): 5V; Features: Compact AC-DC Power Supply; 10 Watt PCB Mount Package; Universal Input Voltage Range; 3000VAC Isolation; Low Output Ripple and Noise; Short Circuit Protected; UL Certified |

| IDT7202LA80TPB | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7202LA80XE | RAC10-SA(-E)(-ST) Series - Powerline Regulated AC-DC Converters; Output Voltage (Vdc): 12V; Features: Compact AC-DC Power Supply; 10 Watt PCB Mount Package; Universal Input Voltage Range; 3000VAC Isolation; Low Output Ripple and Noise; Short Circuit Protected; UL Certified |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7202S50DB | 制造商:IDT/ 功能描述:FIFO, 1K x 9, Asynchronous, 28 Pin, Ceramic, DIP |

| IDT7202SA120P | 制造商:STMicroelectronics 功能描述: 制造商:Integrated Device Technology Inc 功能描述:FIFO, 1K x 9, Asynchronous, 28 Pin, Plastic, DIP 制造商:STMicroelectronics 功能描述:FIFO, 1K x 9, Asynchronous, 28 Pin, Plastic, DIP |

| IDT7202SA35P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT7202SA50D | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:1K X 9 OTHER FIFO, 50 ns, CDIP28 |

| IDT7202SA50P | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:FIFO, 1K x 9, Asynchronous, 28 Pin, Plastic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。