- 您現在的位置:買賣IC網 > PDF目錄377371 > IDT7208L50TDG (Integrated Device Technology, Inc.) CMOS ASYNCHRONOUS FIFO PDF資料下載

參數資料

| 型號: | IDT7208L50TDG |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | CMOS ASYNCHRONOUS FIFO |

| 中文描述: | 異步FIFO的CMOS |

| 文件頁數: | 5/14頁 |

| 文件大小: | 122K |

| 代理商: | IDT7208L50TDG |

5

COMMERCIAL, INDUSTRIAL AND MILITARY

TEMPERATURE RANGES

IDT7203/7204/7205/7206/7207/7208 CMOS ASYNCHRONOUS FIFO

2,048 x 9, 4,096 x 9, 8,192 x 9, 16,384 x 9, 32,768 x 9 and 65,536 x 9

APRIL 3, 2006

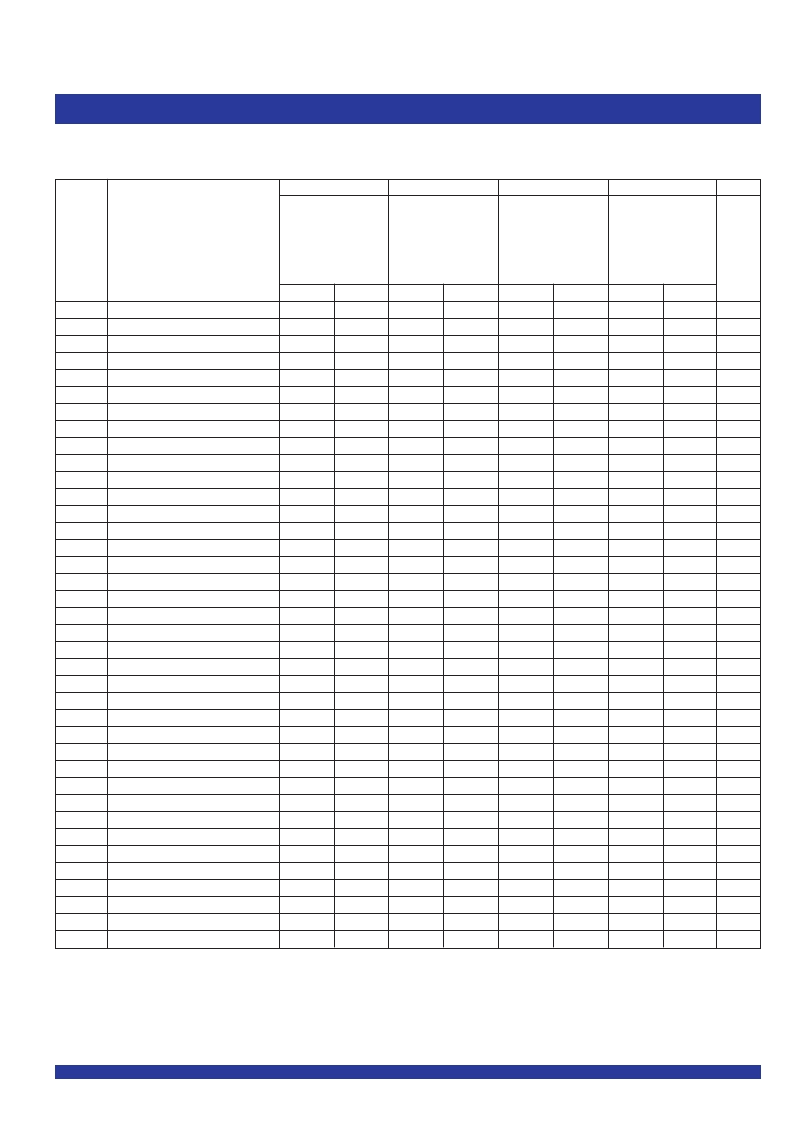

AC ELECTRICAL CHARACTERISTICS

(1)

(CONTINUED)

(Commercial: V

CC

= 5V ± 10%, T

A

= 0

°

C to +70

°

C; Industrial: V

CC

= 5V ± 10%, T

A

= –40

°

C to +85

°

C; Mlitary: V

CC

= 5V ± 10%, T

A

= –55

°

C to +125

°

C)

Mlitary

IDT7203L30

IDT7204L30

IDT7205L30

IDT7206L30

IDT7207L30

NOTES:

1. Timngs referenced as in AC Test Conditions.

2. Pulse widths less than mnimumare not allowed.

3. Values guaranteed by design, not currently tested.

4. Only applies to read data flow-through mode.

Commercial

IDT7203L35

IDT7204L35

IDT7205L35

IDT7206L35

IDT7207L35

IDT7208L35

Mlitary

IDT7203L40

Commercial

IDT7203L50

IDT7204L50

IDT7205L50

IDT7206L50

IDT7207L50

Symbol

f

S

t

RC

t

A

t

RR

t

RPW

t

RLZ

t

WLZ

t

DV

t

RHZ

t

WC

t

WPW

t

WR

t

DS

t

DH

t

RSC

t

RS

t

RSS

t

RTR

t

RTC

t

RT

t

RTS

t

RTR

t

EFL

t

HFH

, t

FFH

t

RTF

t

REF

t

RFF

t

RPE

t

WEF

t

WFF

t

WHF

t

RHF

t

WPF

t

XOL

t

XOH

t

XI

t

XIR

t

XIS

Parameters

Shift Frequency

Read Cycle Time

Access Time

Read Recovery Time

Read Pulse Width

(2)

Read LOW to Data Bus LOW

(3)

Write HIGH to Data Bus Low-Z

(3,4)

Data Valid fromRead HIGH

Read HIGH to Data Bus High-Z

(3)

Write Cycle Time

Write Pulse Width

(2)

Write Recovery Time

Data Set-up Time

Data Hold Time

Reset Cycle Time

Reset Pulse Width

(2)

Reset Set-up Time

(3)

Reset Recovery Time

Retransmt Cycle Time

Retransmt Pulse Width

(2)

Retransmt Set-up Time

(3)

Retransmt Recovery Time

Reset to

EF

LOW

Reset to

HF

and

FF

HIGH

Retransmt LOW to Flags Valid

Read LOW to

EF

LOW

Read HIGH to

FF

HIGH

Read Pulse Width after

EF

HIGH

Write HIGH to

EF

HIGH

Write LOW to

FF

LOW

Write LOW to

HF

Flag LOW

Read HIGH to

HF

Flag HIGH

Write Pulse Width after

FF

HIGH

Read/Write LOW to

XO

LOW

Read/Write HIGH to

XO

HIGH

XI

Pulse Width

(2)

XI

Recovery Time

XI

Set-up Time

Min.

—

40

—

10

30

5

5

5

—

40

30

10

18

0

40

30

30

10

40

30

30

10

—

—

—

—

—

30

—

—

—

—

30

—

—

30

10

10

Max.

25

—

30

—

—

—

—

—

20

—

—

—

—

—

—

—

—

—

—

—

—

—

40

40

40

30

30

—

30

30

40

40

—

30

30

—

—

—

Min.

—

45

—

10

35

5

10

5

—

45

35

10

18

0

45

35

35

10

45

35

35

10

—

—

—

—

—

35

—

—

—

—

35

—

—

35

10

15

Max.

22.22

—

35

—

—

—

—

—

20

—

—

—

—

—

—

—

—

—

—

—

—

—

45

45

45

30

30

—

30

30

45

45

—

35

35

—

—

—

Min.

—

50

—

10

40

5

10

5

—

50

40

10

20

0

50

40

40

10

50

40

40

10

—

—

—

—

—

40

—

—

—

—

40

—

—

40

10

15

Max.

20

—

40

—

—

—

—

—

25

—

—

—

—

—

—

—

—

—

—

—

—

—

50

50

50

35

35

—

35

35

50

50

—

40

40

—

—

—

Min.

—

65

—

15

50

10

15

5

—

65

50

15

30

5

65

50

50

15

65

50

50

15

—

—

—

—

—

50

—

—

—

—

50

—

—

50

10

15

Max.

15

—

50

—

—

—

—

—

30

—

—

—

—

—

—

—

—

—

—

—

—

—

65

65

65

45

45

—

45

45

65

65

—

50

50

—

—

—

Unit

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

相關PDF資料 |

PDF描述 |

|---|---|

| IDT7208L50TDGI | CMOS ASYNCHRONOUS FIFO |

| IDT7208L50TPG | CMOS ASYNCHRONOUS FIFO |

| IDT7208L50TPGI | CMOS ASYNCHRONOUS FIFO |

| IDT7203 | CMOS ASYNCHRONOUS FIFO 2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 |

| IDT7206 | CMOS ASYNCHRONOUS FIFO 2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT72103L120D | 制造商:Integrated Device Technology Inc 功能描述:FIFO, 2K x 9, Asynchronous, 40 Pin, Ceramic, DIP |

| IDT72103S50P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT72104S120P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT72104S50D | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:4K X 9 OTHER FIFO, 50 ns, CDIP40 |

| IDT72104S50P | 制造商:IDT/89'S 功能描述:FIFO, 4K x 9, Asynchronous, 40 Pin, Plastic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復。