- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377397 > IDT72115L50SO (INTEGRATED DEVICE TECHNOLOGY INC) CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72115L50SO |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| 中文描述: | 512 X 16 OTHER FIFO, 50 ns, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁數(shù): | 9/12頁 |

| 文件大?。?/td> | 179K |

| 代理商: | IDT72115L50SO |

5.35

9

COMMERCIAL TEMPERATURE RANGE

IDT72105, IDT72115, IDT72125,

256 x 16, 512 x 16, 1024 x 16 PARALLEL-TO-SERIAL CMOS FIFO

Inputs

FL

Internal Status

Outputs

FF

Mode

RS

DIR

X

0,1

Read Pointer

Location Zero

Increment

(1)

Write Pointer

Location Zero

Increment

(1)

AEF

,

0

X

EF

HF

Reset

Read/Write

0

1

X

X

1

X

1

X

NOTE:

1. Pointer will increment if appropriate flag is HIGH.

2665 tbl 09

Table 1. Reset and First Load Truth Table–Single Device Configuration

3. External logic is needed to generate composite Empty,

Half-Full and Full Flags. This requires the OR-ing of all

EF

,

HF

and

FF

Flags.

4. The Almost-Empty and Almost-Full Flag is not available

due to using the RSOX pin for expansion.

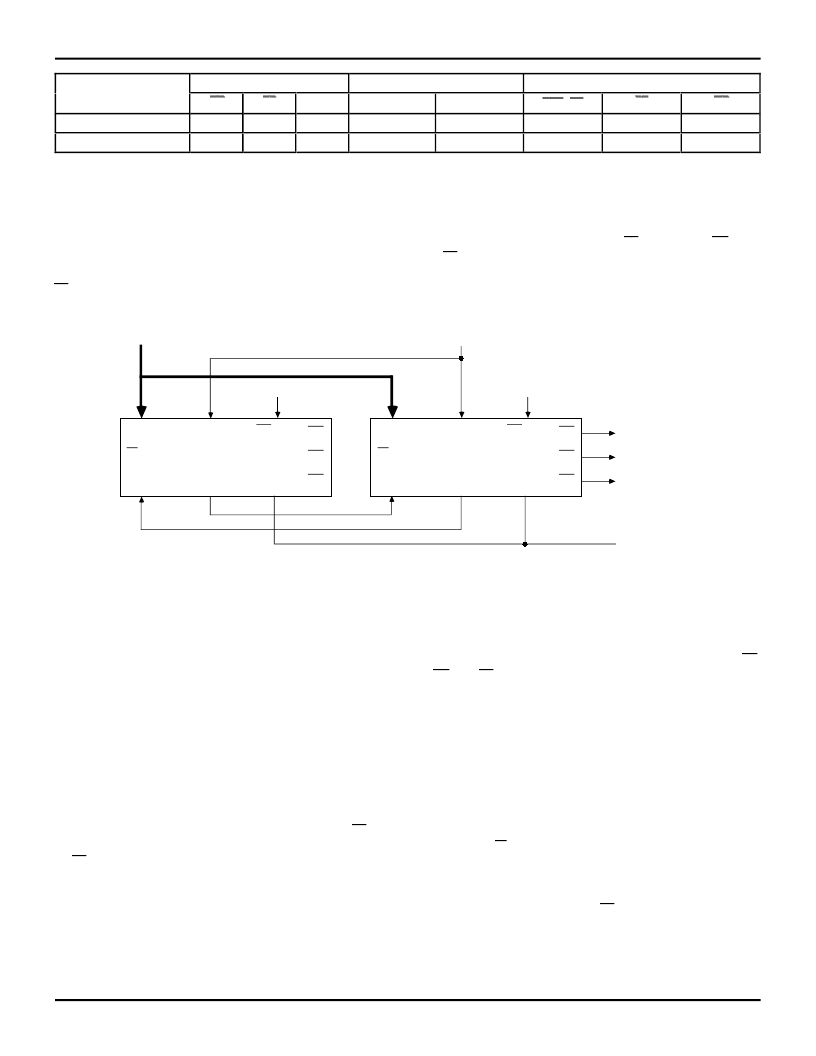

Compound Expansion (Daisy Chain) Mode

The IDT72105/15/25 can be expanded in both depth and

width as Figure 13 indicates:

1. The RSOX-to-RSIX expansion signals are wrapped

around sequentially.

2. The write (

W

) signal is expanded in width.

3. Flag signals are only taken from the Most Significant

Devices.

4. The Least Significant Device in the array must be

programmed with a LOW on

FL

/DIR during reset.

The Serial Data Output (SO) of each device in the serial

word must be tied together. Since the SO pin is three stated,

only the device which is currently shifting out is enabled and

driving the 1-bit bus. NOTE: After reset, the level on the

FL

/DIR pin decides if the Least Significant or Most Significant

Bit is read first out of each device.

The three flag outputs, Empty (

EF

), Half-Full (

HF

) and

Full (

FF

), should be taken from the Most Significant Device (in

the example, FIFO #2). The Almost-Empty/Almost-Full flag is

not available. The RSOX pin is used for expansion.

2665 drw 14

EF

RSIX

RSOX

HF

FF

SOCP

FIFO #2

SO

W

D

16–31

FL/DIR

FULL FLAG

HALF-FULL FLAG

EMPTY FLAG

HIGH AT RESET

SERIAL OUTPUT CLOCK

EF

RSIX

RSOX

HF

FF

SOCP

FIFO #1

SO

W

D

0–15

FL/DIR

LOW AT RESET

SERIAL DATA

PARALLEL DATA

IN

OUT

Figure 11. Width Expansion for 32-bit Parallel Data In

Depth Expansion (Daisy Chain) Mode

The IDT72105/15/25 can easily be adapted to applications

requiring greater than 1024 words. Figure 12 demonstrates

Depth Expansion using three IDT72105/15/25s and an

IDT74FCT138 Address Decoder. Any depth can be attained

by adding additional devices. The Address Decoder is neces-

sary to determine which FIFO is being written. A word of data

must be written sequentially into each FIFO so that the data

will be read in the correct sequence. The IDT72105/15/25

operates in the Depth Expansion Mode when the following

conditions are met:

1. The first device must be programmed by holding

FL

LOW

at Reset. All other devices must be programmed by holding

FL

HIGH at reset.

2. The Read Serial Out Expansion pin (RSOX) of each device

must be tied to the Read Serial In Expansion pin (RSIX) of

the next device (see Figure 12).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72125L50SO | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| IDT72105L50TP | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| IDT72115L50TP | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| IDT72125L50TP | CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16 |

| IDT7210 | 16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72125L25SO | 功能描述:IC FIFO 1KX16 PAR-SER 28SOIC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72125L25SO8 | 功能描述:IC FIFO 1KX16 PAR-SER 28SOIC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72125L25SOG | 功能描述:IC FIFO 1KX16 PAR-SER 28SOIC RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72125L25SOG8 | 功能描述:IC FIFO 1KX16 PAR-SER 28SOIC RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72125L25TP | 功能描述:IC FIFO 1KX16 PAR-SER 28DIP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。