- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377419 > IDT72404L45D (INTEGRATED DEVICE TECHNOLOGY INC) CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72404L45D |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT |

| 中文描述: | 64 X 5 OTHER FIFO, 19 ns, CDIP18 |

| 封裝: | 0.300 INCH, CERDIP-18 |

| 文件頁(yè)數(shù): | 6/9頁(yè) |

| 文件大小: | 95K |

| 代理商: | IDT72404L45D |

5.01

6

IDT72401, IDT72402, IDT72403, IDT72404

CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

TIMING DIAGRAMS (Continued)

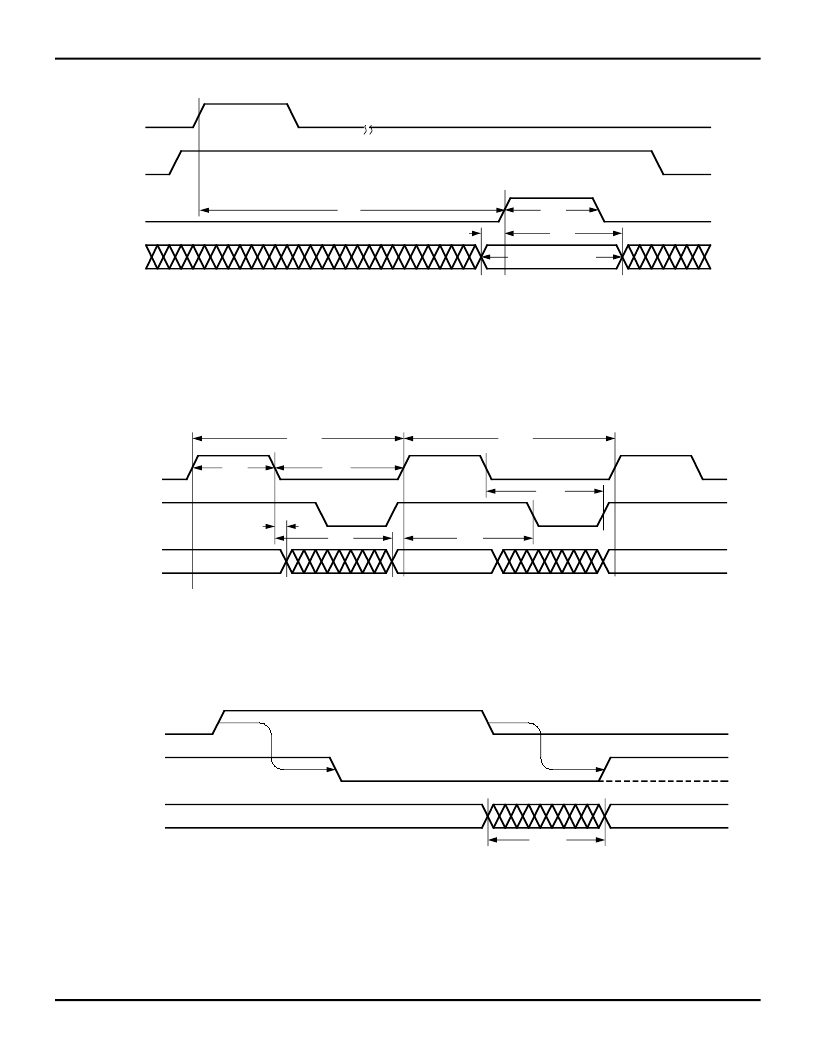

2747 drw 11

SHIFT OUT

OUTPUT DATA

OUTPUT READY

A-DATA

(1)

(2)

(3)

(4)

(5)

(6)

(7)

B-DATA

A or B

Figure 6. The Mechanism of Shifting Data Out of the FIFO

NOTES:

1. Output Ready HIGH indicates that data is available and a Shift Out pulse may be applied.

2. Shift Out goes HIGH causing the next step.

3. Output Ready goes LOW.

4. The read pointer is incremented.

5. Output Ready goes HIGH indicating that new data (B) is now available at the FIFO outputs.

6. If the FIFO has only one word loaded (A DATA) then Output Ready stays LOW and the A DATA remains unchanged at the outputs.

7. Shift Out pulses applied when Output Ready is LOW will be ignored.

2747 drw 10

SHIFT OUT

OUTPUT DATA

OUTPUT READY

t

SOH

1/f

OUT

t

SOL

1/f

OUT

t

ORH

t

ORL

t

ODS

A-DATA

B-DATA

(1)

t

ODH

C-DATA

(2)

NOTES:

1. This data is loaded consecutively A, B, C.

2. Data is shifted out when Shift Out makes a HIGH to LOW transition.

Figure 5. Output TIming

2747 drw 09

SHIFT IN

INPUT DATA

INPUT READY

STABLE DATA

(1)

(3)

(4)

(5)

SHIFT OUT

(2)

t

IPH

t

HIR

t

SIR

t

PT

NOTES:

1. FIFO is initially full.

2. Shift Out pulse is applied.

3. Shift In is held HIGH.

4. As soon as Input Ready becomes HIGH the Input Data is loaded into the FIFO.

5. The write pointer is incremented. Shift In should not go LOW until (t

PT

+ t

IPH

).

Figure 4. Data is Shifted In Whenever Shift In and Input Ready are Both HIGH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72404L45DB | CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT |

| IDT72404L45P | CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT |

| IDT72413 | High-Performance Current-Mode PWM Controller 14-SOIC 0 to 70 |

| IDT72413L25D | High-Performance Current-Mode PWM Controller 8-SOIC 0 to 70 |

| IDT72413L25DB | High-Performance Current-Mode PWM Controller 14-SOIC 0 to 70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72413L25P | 功能描述:IC FIFO PAR W/FLAGS 32KB 20DIP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72413L25SO | 功能描述:IC FIFO PAR W/FLAGS 32KB 20SOIC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72413L25SO8 | 功能描述:IC FIFO PAR W/FLAGS 32KB 20SOIC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72413L25SOG | 功能描述:IC FIFO PAR W/FLAGS 32KB 20SOIC RoHS:是 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72413L25SOG8 | 功能描述:IC FIFO PAR W/FLAGS 32KB 20SOIC RoHS:是 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。