- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10008 > IDT72845LB15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC DL 4096X18 128TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72845LB15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 23/26頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC DL 4096X18 128TQFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 72K(4K x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時(shí)間: | 15ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72845LB15PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

6

JANUARY 13, 2009

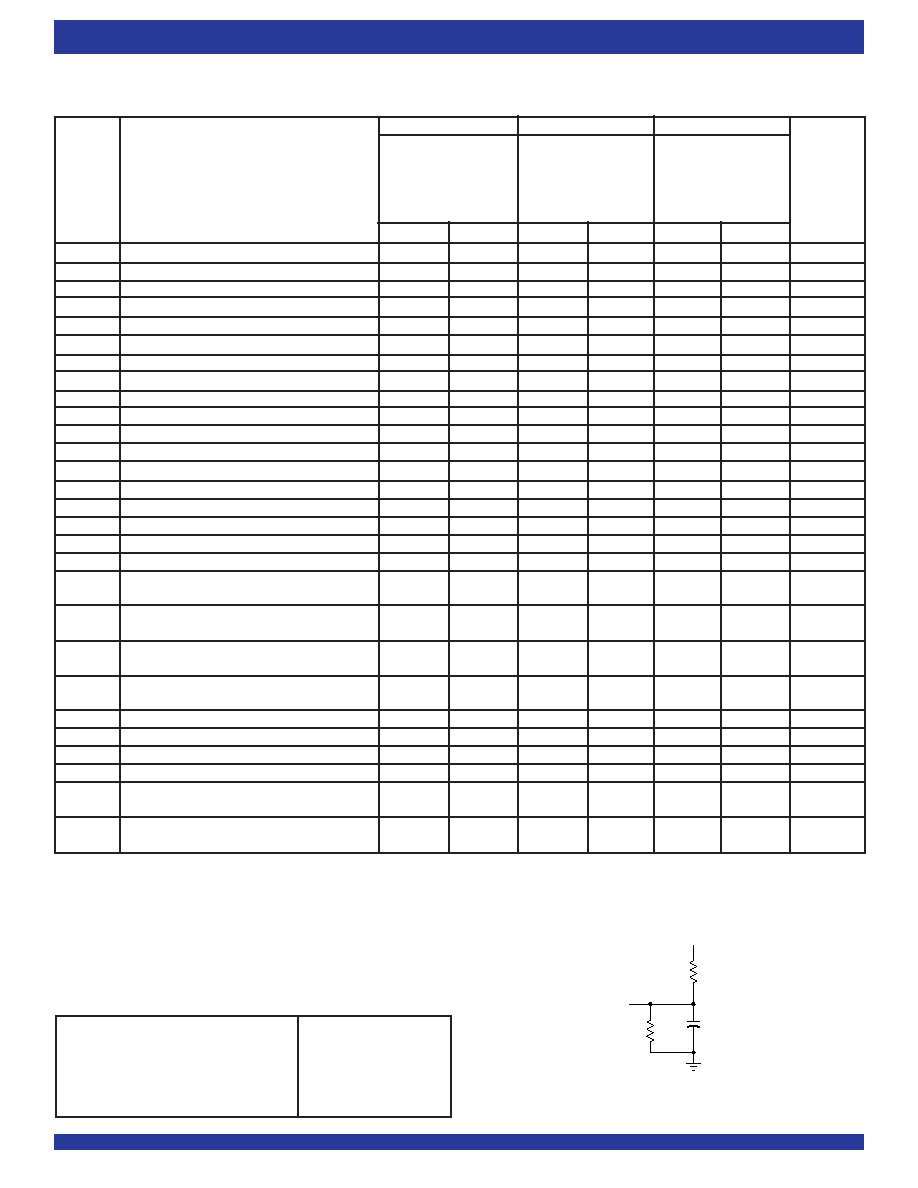

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0

°C to +70°C; Industrial: VCC = 5V ± 10%, TA = -40°C + 85°C)

Input Pulse Levels

GND to 3.0V

Input Rise/Fall Times

3ns

Input Timing Reference Levels

1.5V

Output Reference Levels

1.5V

Output Load

See Figure 1

AC TEST CONDITIONS

Figure 1. Output Load

* Includes jig and scope capacitances.

Commercial

Com’l & Ind’l(1)

Commercial

IDT72805LB10

IDT72805LB15

IDT72805LB25

IDT72815LB10

IDT72815LB15

IDT72815LB25

IDT72825LB10

IDT72825LB15

IDT72825LB25

IDT72835LB10

IDT72835LB15

IDT72835LB25

IDT72845LB10

IDT72845LB15

IDT72845LB25

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Unit

fS

Clock Cycle Frequency

—

100

—

66.7

—

40

MHz

tA

Data Access Time

2

6.5

2

10

3

15

ns

tCLK

Clock Cycle Time

10

—

15

—

25

—

ns

tCLKH

Clock HIGH Time

4.5

—

6

—

10

—

ns

tCLKL

Clock LOW Time

4.5

—

6

—

10

—

ns

tDS

Data Setup Time

3

—

4

—

6

—

ns

tDH

Data Hold Time

0

—

1

—

1

—

ns

tENS

Enable Setup Time

3

—

4

—

6

—

ns

tENH

Enable Hold Time

0

—

1

—

1

—

ns

tRS

Reset Pulse Width(2)

10—15—25

—

ns

tRSS

Reset Setup Time

8

—

10

—

15

—

ns

tRSR

Reset Recovery Time

8

—

10

—

15

—

ns

tRSF

Reset to Flag and Output Time

—

15

—

15

—

25

ns

tOLZ

Output Enable to Output in Low-Z(3)

0—0—0

—

ns

tOE

Output Enable to Output Valid

—

6

—

8

—

12

ns

tOHZ

Output Enable to Output in High-Z(3)

16181

12

ns

tWFF

Write Clock to Full Flag

—

6.5

—

10

—

15

ns

tREF

Read Clock to Empty Flag

—

6.5

—

10

—

15

ns

tPAFA

Clock to Asynchronous Programmable

—

17

—

20

—

35

ns

Almost-Full Flag

tPAFS

Write Clock to Synchronous

—

8

—

10

—

12

ns

Programmable Almost-Full Flag

tPAEA

Clock to Asynchronous Programmable

—

17

—

20

—

35

ns

Almost-Empty Flag

tPAES

Read Clock to Synchronous

—

8

—

10

—

12

ns

Programmable Almost-Empty Flag

tHF

Clock to Half-Full flag

—

17

—

20

—

35

ns

tXO

Clock to Expansion Out

—

6.5

—

10

—

15

ns

tXI

Expansion In Pulse Width

3

—

6.5

—

10

—

ns

tXIS

Expansion In Setup Time

3

—

—

10

—

ns

tSKEW1

Skew time between Read Clock &

5

—

6

—

10

—

ns

Write Clock for

FF/IR and EF/OR

tSKEW2(4)

Skew time between Read Clock &

12

—

15

—

17

—

ns

Write Clock for

PAE and PAF

3139 drw 03

30pF*

1.1K

5V

D.U.T.

680

NOTES:

1. Industrial Temperature Range Product for the 15ns speed grade is available as a standard device.

2. Pulse widths less than minimum values are not allowed.

3. Values guaranteed by design, not currently tested.

4. tSKEW2 applies to synchronous

PAE and synchronous PAF only.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27497T10A35SD | CONN RCPT 13POS WALL MNT W/SCKT |

| IDT72V821L15PF | IC FIFO SYNC 512X9X2 15NS 64QFP |

| IDT72V815L15PF | IC FIFO SYNC 512X18 15NS 128QFP |

| IDT72815LB15PF | IC FIFO SYNC DUAL 512X18 128TQFP |

| IDT72V821L15TF | IC FIFO SYNC 512X9X2 15NS 64QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72845LB15PFI | 功能描述:IC FIFO SYNC DL 4096X18 128TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72845LB15PFI8 | 功能描述:IC FIFO SYNC DL 4096X18 128TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72845LB25PF | 功能描述:IC FIFO SYNC DL 4096X18 128TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72845LB25PF8 | 功能描述:IC FIFO SYNC DL 4096X18 128TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT7284L12PA | 功能描述:IC FIFO 2048X18 12NS 56TSSOP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。