- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10043 > IDT72V251L15J (IDT, Integrated Device Technology Inc)IC FIFO SYNC 4096X18 15NS 32PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V251L15J |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 7/14頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 4096X18 15NS 32PLCC |

| 標(biāo)準(zhǔn)包裝: | 32 |

| 系列: | 72V |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 72K(4K x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時(shí)間: | 15ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 32-PLCC(13.97x11.43) |

| 包裝: | 管件 |

| 其它名稱: | 72V251L15J |

IDT72V201/72V211/72V221/72V231/72V241/72V251 3.3V CMOS SyncFIFO

256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

2

Symbol

Name

I/O

Description

D0-D8

DataInputs

I

Data inputs for a 9-bit bus.

RS

Reset

I

When RS is set LOW, internal read and write pointers are set to the first location of the RAM array, FF

and PAF go HIGH, and PAE and EF go LOW. A Reset is required before an initial Write after power-up.

WCLK

WriteClock

I

Data is written into the FIFO on a LOW-to-HIGH transition of WCLK when the Write Enable(s) are asserted.

WEN1

WriteEnable1

I

If the FIFO is configured to have programmable flags, WEN1 is the only Write Enable pin. When WEN1 is

LOW, data is written into the FIFO on every LOW-to-HIGH transition WCLK. If the FIFO is configured to

have two write enables, WEN1 must be LOW and WEN2 must be HIGH to write data into the FIFO. Data

will not be written into the FIFO if the FF is LOW.

WEN2/LD

WriteEnable2/

I

The FIFO is configured at Reset to have either two write enables or programmable flags. If WEN2/LD

Load

is HIGH at Reset, this pin operates as a second write enable. If WEN2/LD is LOW at Reset, this pin operates

as a control to load and read the programmable flag offsets. If the FIFO is configured to have two write

enables, WEN1 must be LOW and WEN2 must be HIGH to write data into the FIFO. Data will not be written

into the FIFO if the FF is LOW. If the FIFO is configured to have programmable flags, WEN2/LD is held LOW to

writeorreadtheprogrammableflagoffsets.

Q0-Q8

DataOutputs

O

Data outputs for a 9-bit bus.

RCLK

Read Clock

I

Data is read from the FIFO on a LOW-to-HIGH transition of RCLK when REN1 and REN2 are asserted.

REN1

Read Enable 1

I

When REN1 and REN2 are LOW, data is read from the FIFO on every LOW-to-HIGH transition of RCLK. Data

will not be read from the FIFO if the EF is LOW.

REN2

Read Enable 2

I

When REN1 and REN2 are LOW, data is read from the FIFO on every LOW-to-HIGH transition of RCLK.

Data will not be read from the FIFO if the EF is LOW.

OE

OutputEnable

I

When OE is LOW, the data output bus is active. If OE is HIGH, the output data bus will be in a high-impedance

state.

EF

EmptyFlag

O

When EF is LOW, the FIFO is empty and further data reads from the output are inhibited. When EF is

HIGH, the FIFO is not empty. EF is synchronized to RCLK.

PAE

Programmable

O

When PAE is LOW, the FIFO is almost-empty based on the offset programmed into the FIFO. The default

Almost-EmptyFlag

offset at reset is Empty+7. PAE is synchronized to RCLK.

PAF

Programmable

O

When PAF is LOW, the FIFO is almost-full based on the offset programmed into the FIFO. The default

Almost-FullFlag

offset at reset is Full-7. PAF is synchronized to WCLK.

FF

Full Flag

O

When FF is LOW, the FIFO is full and further data writes into the input are inhibited. When FF is HIGH, the FIFO

is not full. FF is synchronized to WCLK.

VCC

Power

One 3.3V volt power supply pin.

GND

Ground

One 0 volt ground pin.

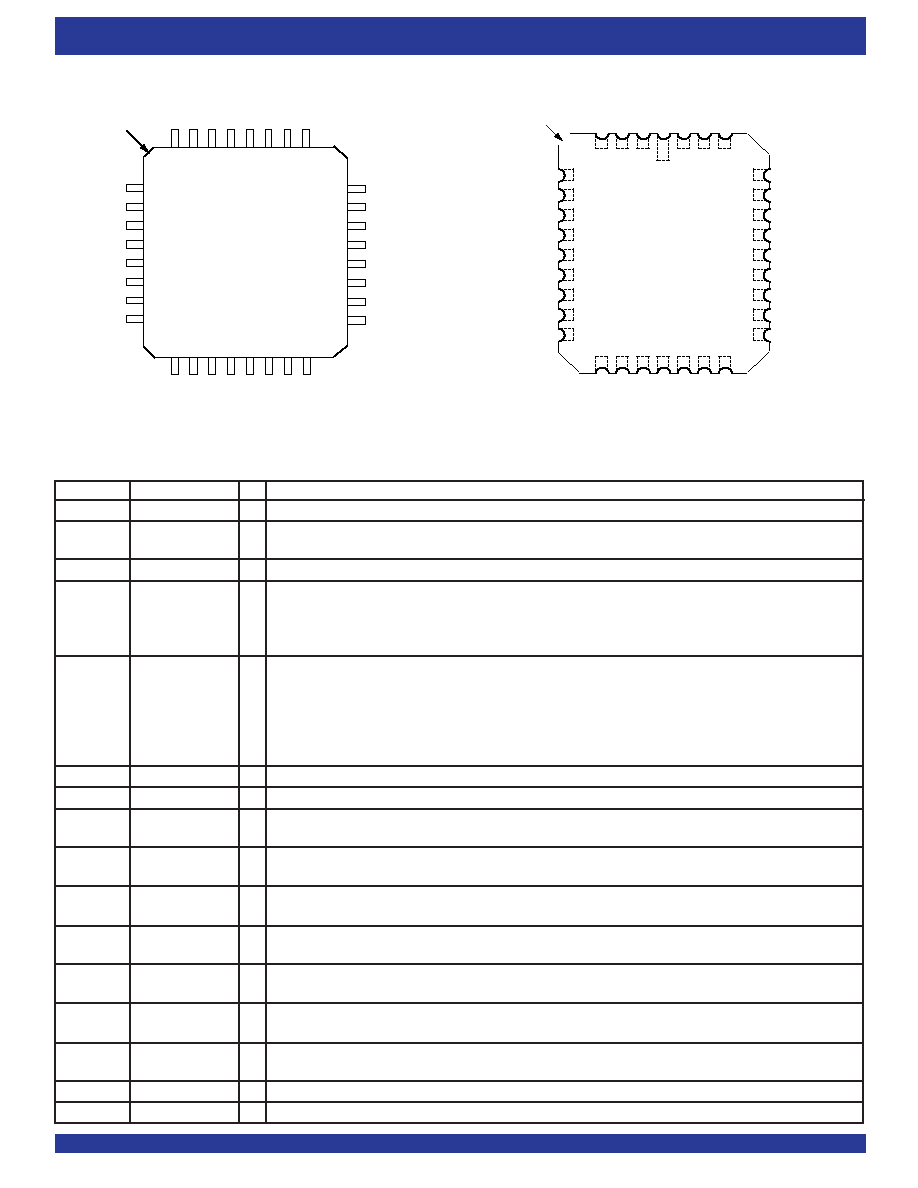

TQFP (PR32-1, order code: PF)

TOP VIEW

PLCC (J32-1, order code: J)

TOP VIEW

PIN CONFIGURATION

RS

WEN1

WCLK

WEN2/

LD

V

Q8

Q7

Q6

Q5

5

6

7

8

16

CC

D1

PAF

PAE

GND

REN1

RCLK

REN2

D0

27 26 25

24

23

22

21

29 28

32 31 30

9 1011 1213 1415

D

2

3

4

5

6

D

7

8

4092 drw02

Q

3

Q

4

Q

2

Q

1

Q

0

EF

OE

FF

1

2

3

4

20

19

18

17

INDEX

RS

WEN1

WCLK

WEN2/

LD

VCC

Q8

Q7

Q6

Q5

5

6

7

8

9

10

11

12

13

D1

PAF

PAE

GND

REN1

RCLK

REN2

OE

D0

27

26

25

24

23

22

21

29

28

432

1

32 31 30

14 15 16 17 18 19 20

D

2

D

3

D

4

D

5

D

6

D

7

D

8

Q

3

Q

4

Q

2

Q

1

Q

0

FF

EF

INDEX

4092 drw02a

PIN DESCRIPTIONS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27472E18C32P | CONN RCPT 32POS WALL MT W/PINS |

| IDT72251L25JI | IC FIFO SYNC 512X9 25NS 32PLCC |

| LT1134AIN | IC 4DRV/4RCV RS232 5V 24-DIP |

| VI-2V0-MY | CONVERTER MOD DC/DC 5V 50W |

| LTC1327CG#PBF | IC TXRX EIA/TIA-562 3.3V 28-SSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V251L15J8 | 功能描述:IC FIFO SYNC 4096X18 15NS 32PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72V251L15JGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 4096X18 15NS 32PLCC |

| IDT72V251L15JGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 4096X18 15NS 32PLCC |

| IDT72V251L15JI | 功能描述:IC FIFO SYNC 4096X18 15NS 32PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V251L15JI8 | 功能描述:IC FIFO SYNC 4096X18 15NS 32PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。