- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10016 > IDT72V3640L10PF8 (IDT, Integrated Device Technology Inc)IC FIFO SS 1024X36 10NS 128-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V3640L10PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 39/46頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO SS 1024X36 10NS 128-TQFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 72V |

| 功能: | 異步,同步 |

| 存儲(chǔ)容量: | 36.8K(1K x 36) |

| 數(shù)據(jù)速率: | 100MHz |

| 訪問時(shí)間: | 10ns |

| 電源電壓: | 3.15 V ~ 3.45 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V3640L10PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

44

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36 and 32,768 x 36

OCTOBER 22, 2008

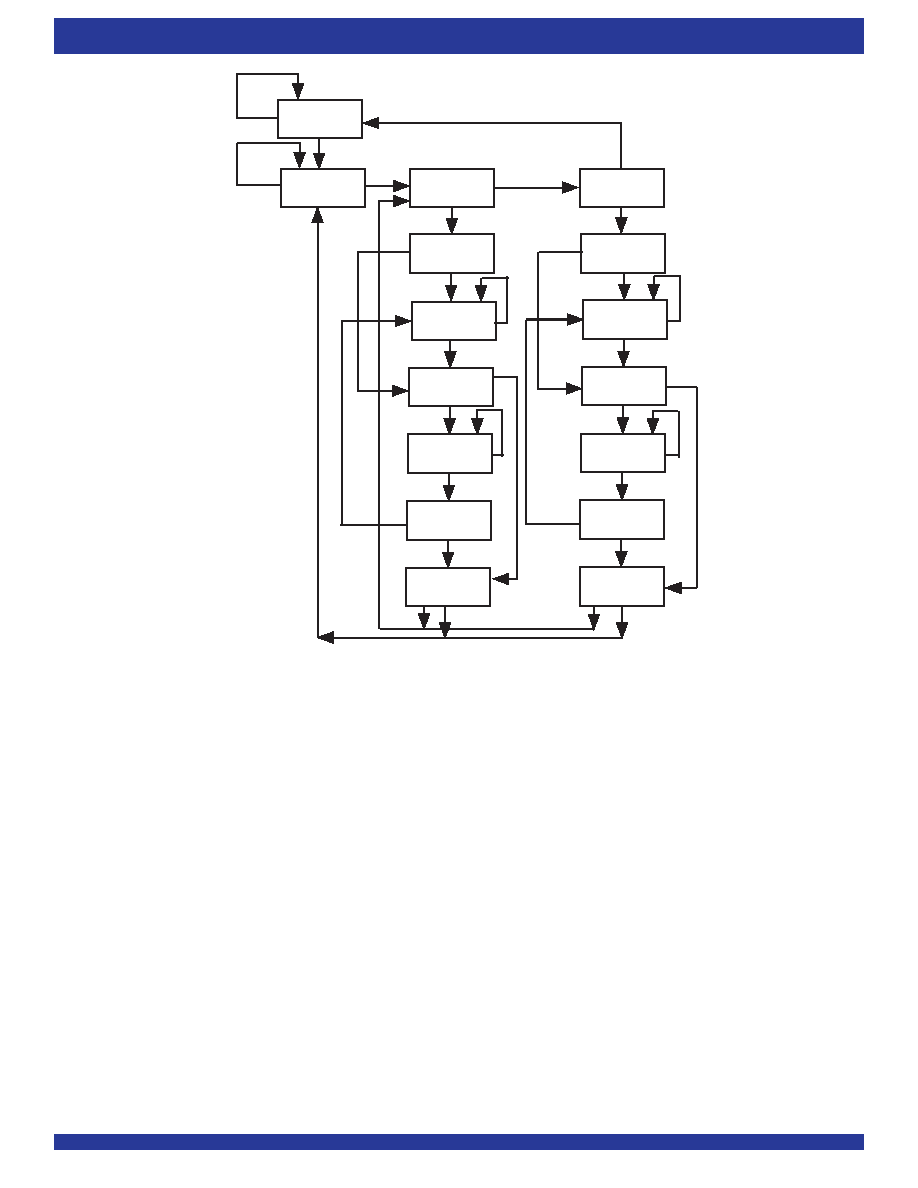

Figure 33. TAP Controller State Diagram

Test-Logic

Reset

Run-Test/

Idle

1

0

Select-

DR-Scan

Select-

IR-Scan

1

Capture-IR

0

Capture-DR

0

EXit1-DR

1

Pause-DR

0

Exit2-DR

1

Update-DR

1

Exit1-IR

1

Exit2-IR

1

Update-IR

1

0

1

4667 drw38

0

Shift-DR

0

Shift-IR

0

Pause-IR

0

1

Input = TMS

0

1

Refer to the IEEE Standard Test Access Port Specification (IEEE Std.

1149.1) for the full state diagram

All state transitions within the TAP controller occur at the rising edge of the

TCLK pulse. The TMS signal level (0 or 1) determines the state progression

that occurs on each TCLK rising edge. The TAP controller takes precedence

over the FIFO memory and must be reset after power up of the device. See

TRST description for more details on TAP controller reset.

CAPTURE-DR

Data is loaded from the parallel input pins or core outputs into the Data

Register.

SHIFT-DR

Thepreviouslycaptureddataisshiftedinserially,LSBfirstattherisingedge

ofTCLKintheTDI/TDOpathandshiftedoutserially,LSBfirstatthefallingedge

of TCLK towards the output.

UPDATE-DR

The shifting process has been completed. The data is latched into their

parallel outputs in this state to be accessed through the internal bus.

EXIT1-DR / EXIT2-DR

Thisisatemporarycontrollerstate.IfTMSisheldhigh,arisingedgeapplied

toTCKwhileinthisstatecausesthecontrollertoentertheUpdate-DRstate.This

terminates the scanning process. All test data registers selected by the current

instruction retain their previous state unchanged.

PAUSE-DR

This controller state allows shifting of the test data register in the serial path

between TDI and TDO to be temporarily halted. All test data registers selected

by the current instruction retain their previous state unchanged.

Capture-IR, Shift-IR and Update-IR, Exit-IR and Pause-IR are

similartoDataregisters.Theseinstructionsoperateontheinstructionregisters.

NOTES:

1. Five consecutive TCK cycles with TMS = 1 will reset the TAP.

2. TAP controller does not automatically reset upon power-up. The user must provide a reset to the TAP controller (either by

TRST or TMS).

3. TAP controller must be reset before normal FIFO operations can begin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27499E12B3PA | CONN RCPT 3POS BOX MNT W/PINS |

| XRT6164AIDTR-F | IC TXRX DGTL INTERFACE 16SOIC |

| MS27497T10B13S | CONN RCPT 13POS WALL MNT W/SCKT |

| SY88927VZG | IC AMP DIFF REC 2.5GBPS 3.3V/5V |

| IDT72V3634L15PF8 | IC FIFO 512X36X2 15NS 128QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V3640L15PF | 功能描述:IC FIFO SS 1024X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L15PF8 | 功能描述:IC FIFO SS 1024X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L15PFI | 功能描述:IC FIFO SS 1024X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L15PFI8 | 功能描述:IC FIFO SS 1024X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L6BB | 功能描述:IC FIFO SS 1024X36 6NS 144-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。