- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9980 > IDT72V3641L20PF (IDT, Integrated Device Technology Inc)IC SYNCFIFO 1024X36 20NS 120TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V3641L20PF |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 11/21頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SYNCFIFO 1024X36 20NS 120TQFP |

| 標(biāo)準(zhǔn)包裝: | 45 |

| 系列: | 72V |

| 功能: | 異步,同步 |

| 存儲(chǔ)容量: | 36.8K(1K x 36) |

| 數(shù)據(jù)速率: | 520Mbs |

| 訪問(wèn)時(shí)間: | 20ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 120-LQFP |

| 供應(yīng)商設(shè)備封裝: | 120-TQFP(14x14) |

| 包裝: | 托盤(pán) |

| 其它名稱: | 72V3641L20PF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

19

COMMERCIALTEMPERATURERANGE

IDT72V3631/72V3641/72V3651

3.3V CMOS SYNCFIFO 512 x 36, 1,024 x 36 and 2,048 x 36

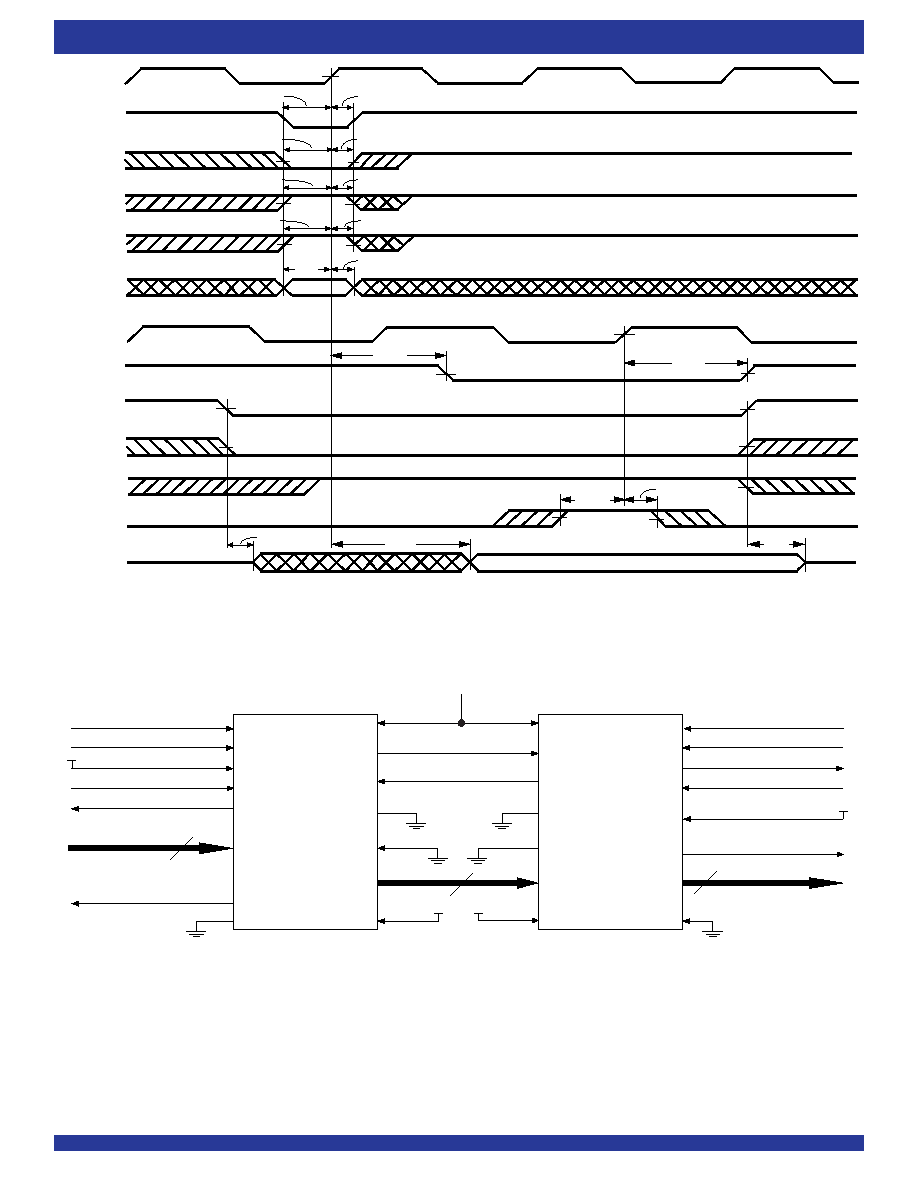

Figure 16. Timing for

Mail2

Mail2 Register and MBF2

MBF2

MBF2 Flag

Figure 17. Block Diagram of 512 x 36, 1,024 x 36, 2,048 x 36 Synchronous FIFO Memory with

Programmable Flags used in Depth Expansion Configuration

NOTES:

1. Mailbox feature is not supported in depth expansion applications. (MBA + MBB tie to GND)

2. Transfer clock should be set either to the Write Port Clock (CLKA) or the Read Port Clock (CLKB), whichever is faster.

3. Retransmit feature is not supported in depth expansion applications.

4. The amount of time it takes for OR of the last FIFO in the chain to go HIGH (i.e. valid data to appear on the last FIFO’s outputs) after a word has been written to the first FIFO is the sum

of the delays for each individual FIFO: (N - 1)*(4*transfer clock) + 3*TRCLK, where N is the number of FIFOs in the expansion and TRCLK is the CLKB period.

5. The amount of time is takes for IR of the first FIFO in the chain to go HIGH after a word has been read from the last FIFO is the sum of the delays for each individual FIFO: (N -

1)*(3*transfer clock) + 2*TWCLK, where N is the number of FIFOs in the expansion and TWCLK is the CLKA period.

4658 drw 19

CLKB

ENB

B0 - B35

MBB

CSB

W/RB

CLKA

MBF2

CSA

MBA

ENA

A0 - A35

W/

RA

W1

tENS2

tENH2

tDS

tDH

tPMF

tENS1

tENH1

tDIS

tEN

tPMR

W1 (Remains valid in Mail2 Register after read)

tENS2

tENH2

tENS2

tENH2

tENS2

tENH2

DATA IN (Dn)

READ CLOCK (CLKB)

READ ENABLE (ENB)

OUTPUT READY (OR)

CHIP SELECT (

CSB)

DATA OUT (Qn)

TRANSFER CLOCK

4658 drw 20

IDT

72V3631

72V3641

72V3651

VCC

WRITE

READ

A0-A35

MBA

CHIP SELECT (

CSA)

WRITE SELECT (W/

RA)

WRITE ENABLE (ENA)

ALMOST-FULL FLAG (

AF)

INPUT READY (IR)

WRITE CLOCK (CLKA)

CLKB

OR

ENB

CSB

B0-B35

W/

RB

MBB

CLKA

ENA

IR

CSA

MBA

A0-A35

W/

RA

READ SELECT (W/

RB)

ALMOST-EMPTY FLAG (

AE)

B0-B35

MBB

n

Qn

Dn

VCC

IDT

72V3631

72V3641

72V3651

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| D38999/26WA98PD | CONN PLUG 3POS STRAIGHT W/PINS |

| MS27468T21A41S | CONN RCPT 41POS JAM NUT W/SCKT |

| MS27467T9B35S EDR | CONN PLUG 6POS STRAIGHT W/SCKT |

| D38999/20WF32SA | CONN RCPT 32POS WALL MNT W/SCKT |

| VI-J63-MX-S | CONVERTER MOD DC/DC 24V 75W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V3641L20PF8 | 功能描述:IC SYNCFIFO 1024X36 20NS 120TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V3641L20PQF | 功能描述:IC SYNCFIFO 1024X36 20NS 132PQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V3642L10PF | 功能描述:IC FIFO SYNC 3.3V CMOS 120-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V3642L10PF8 | 功能描述:IC FIFO 1MX72 10NS 120QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V3642L10PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 3.3V CMOS 120-TQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。