- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄10037 > IDT72V821L15TF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 512X9X2 15NS 64QFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V821L15TF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 16/16頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 512X9X2 15NS 64QFP |

| 標(biāo)準(zhǔn)包裝: | 1,250 |

| 系列: | 72V |

| 功能: | 異步 |

| 存儲(chǔ)容量: | 9.2K(512 x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問(wèn)時(shí)間: | 15ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 其它名稱(chēng): | 72V821L15TF8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)

9

IDT72V801/72V8211/72V821/72V831/72V841/72V851 3.3V DUAL CMOS SyncFIFOTM

DUAL 256 x 9, DUAL 512 x 9, DUAL 1K x 9, DUAL 2K x 9, DUAL 4K x 9, DUAL 8K x 9

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

OCTOBER 22, 2008

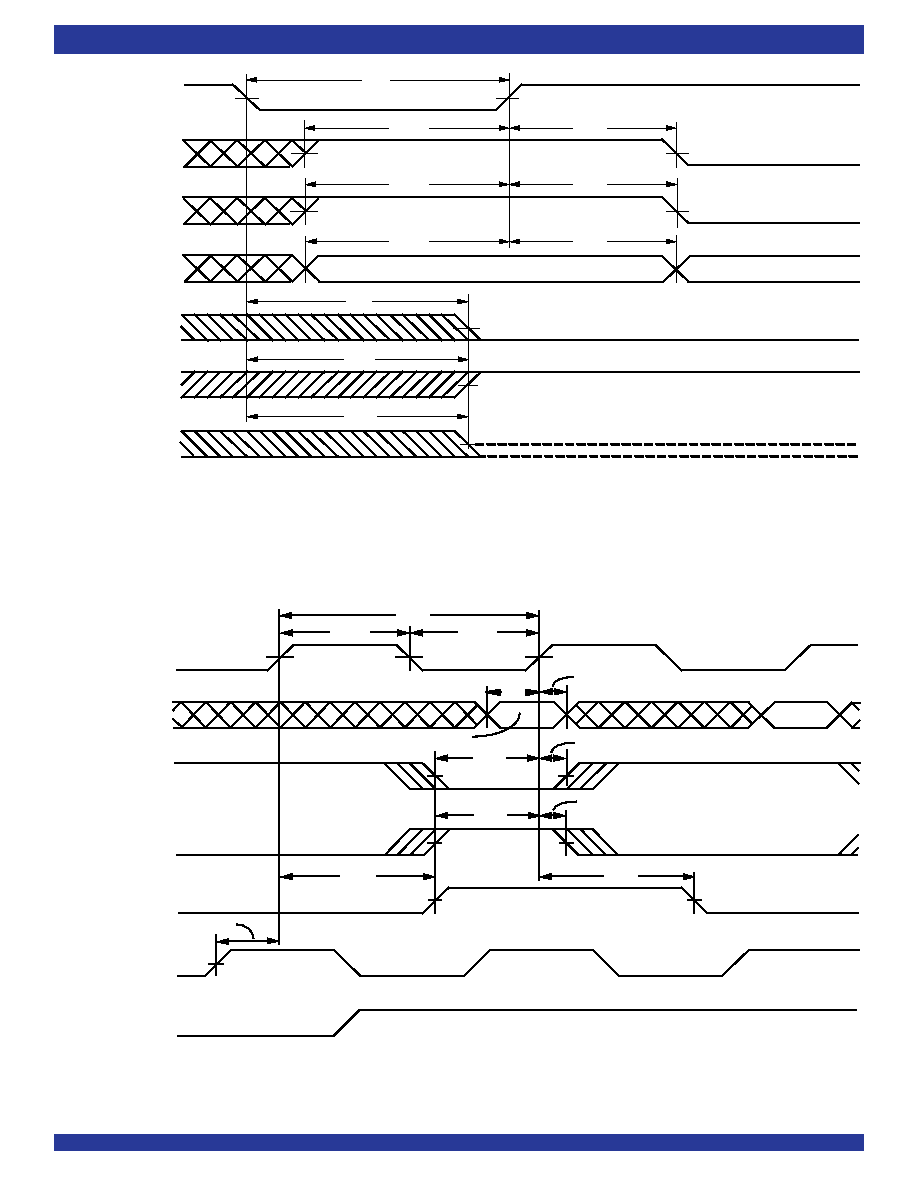

Figure 4. Reset Timing

NOTES:

1. Holding WENA2/

LDA (WENB2/LDB) HIGH during reset will make the pin act as a second Write Enable pin. Holding WENA2/LDA (WENB2/LDB) LOW during reset will make

the pin act as a load enable for the programmable flag offset registers.

2. After reset, QA0 - QA8 (QB0 - QB8) will be LOW if

OEA (OEB) = 0 and tri-state if OEA (OEB) = 1.

3. The clocks RCLKA, WCLKA (RCLKB, WCLKB) can be free-running during reset.

Figure 5. Write Cycle Timing

NOTE:

1. tSKEW1 is the minimum time between a rising RCLKA (RCLKB) edge and a rising WCLKA (WCLKB) edge for

FFA (FFB) to change during the current clock cycle. If the time

between the rising edge of RCLKA (RCLKB) and the rising edge of WCLKA (WCLKB) is less than tSKEW1, then

FFA (FFB) may not change state until the next WCLKA (WCLKB)

edge.

tDH

tENH

tSKEW1(1)

tCLK

tCLKH

tCLKL

tDS

tENS

tWFF

WCLKA (WCLKB)

(DA0 - DA8

DB0 - DB8)

WENA1

(WENB1)

WENA2 (WENB2)

(If Applicable)

FFA

(FFB)

RCLKA (RCLKB)

RENA1, RENA2

(RENB1, RENB2)

NO OPERATION

4093 drw 07

DATA IN VALID

tENS

tENH

tRS

tRSR

RSA (RSB)

RENA1, RENA2

(RENB1, RENB2)

tRSF

OEA (OEB) = 1

OEA (OEB) = 0

(2)

EFA, PAEA

(EFB, PAEB)

FFA, PAFA

(FFA, PAFA)

QA0 - QA8

(QB0 - QB8)

4093 drw 06

WENA1

(WENB1)

tRSS

tRSF

tRSR

tRSS

tRSR

tRSS

WENA2/LDA

(WENB2/LDB)

(1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72V815L15PF8 | IC FIFO SYNC 512X18 15NS 128QFP |

| IDT72815LB15PF8 | IC FIFO SYNC DUAL 512X18 128TQFP |

| VI-BNR-IV-F3 | CONVERTER MOD DC/DC 7.5V 150W |

| VI-B5Z-MY | CONVERTER MOD DC/DC 2V 20W |

| VI-BNR-IV-F2 | CONVERTER MOD DC/DC 7.5V 150W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V821L15TFI | 功能描述:IC FIFO SYNC 512X9X2 15NS 64QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT72V821L15TFI8 | 功能描述:IC FIFO SYNC 512X9X2 15NS 64QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT72V821L20PF | 功能描述:IC FIFO SYNC 512X9X2 20NS 64QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT72V821L20PF8 | 功能描述:IC FIFO SYNC 512X9X2 20NS 64QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT72V821L20TF | 功能描述:IC FIFO SYNC 512X9X2 20NS 64QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。