- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425G30S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425G30S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 8/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST425G30S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

IMS T400

/ 74

8

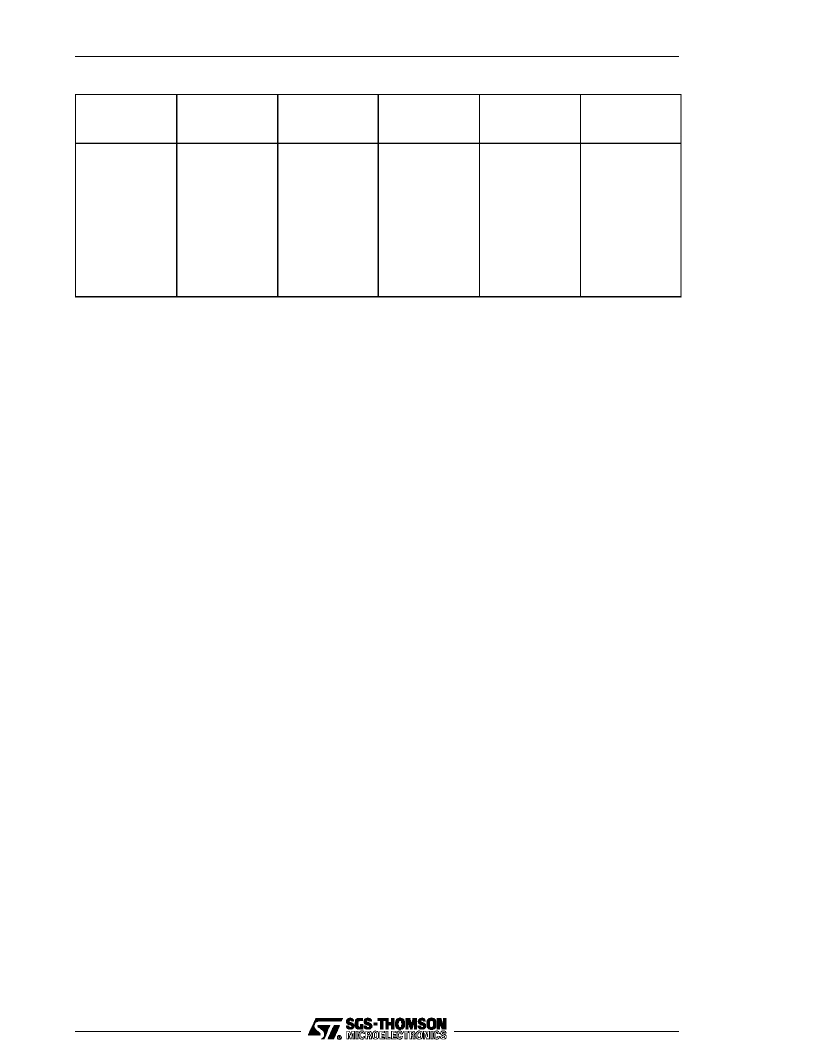

ProcSpeed-

Select2

ProcSpeed-

Select1

ProcSpeed-

Select0

Processor

Clock

Speed MHz

20.0

22.5

25.0

30.0

35.0

Processor

Cycle

Time ns

50.0

44.4

40.0

33.3

28.6

Notes

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Not supported

Not supported

Not supported

Not supported

Invalid

Not supported

Invalid

17.5

57.1

Table 3.2

Processor speed selection

3.5

Bootstrap

ThetransputercanbebootstrappedeitherfromalinkorfromexternalROM.Tofacilitatedebugging,

Boot-

FromROM

maybedynamicallychangedbutmustobeythespecifiedtimingrestrictions.Itissampledonce

only by the transputer,before the first instruction is executed after

Reset

is taken low.

If

BootFromROM

is connected high (e.g. to

VDD

) the transputer starts to execute code from thetop two

bytes in externalmemory,at address#7FFFFFFE. Thislocationshould containa backwardjump toa pro-

gram in ROM. Following this access,

BootFromROM

may be taken low if required. The processor is in

the low priority state, and the

W

register points to MemStart (page 4).

If

BootFromROM

is connected low (e.g. to

GND

) the transputer will wait for the first bootstrap message

toarriveonanyone ofitslinks.Thetransputerisreadytoreceivethefirstbyteonalinkwithintwoprocessor

cycles

TPCLPCL

after

Reset

goes low.

If the first byte received (the control byte) is greater than 1 it is taken as the quantity of bytes to be input.

The followingbytes,tothat quantity,are then placedin internalmemory startingat locationMemStart.Fol-

lowing reception of the last byte thetransputer willstart executing code at MemStartas a low priority pro-

cess.

BootFromROM

may be taken high after reception of the last byte, if required. The memory space

immediately abovethe loadedcodeisused asworkspace.Abytearrivingontheotherlinkafterthecontrol

byte has beenreceived and on thebootstrapping linkafter the last bootstrapbyte, will be retainedand no

acknowledge will be sent until a process inputs from them.

3.6

Peek and poke

Any locationin internalorexternal memorycan beinterrogated and altered whenthetransputer is waiting

for a bootstrap fromlink. If the control byte is 0 then eight more bytes are expectedon the same link. The

first four byteword istaken asan internalor externalmemory addressat whichto poke (write) thesecond

four byteword.Ifthecontrol byteis 1 thenextfour bytesare usedas theaddressfromwhich topeek (read)

a word of data; the word is sent down the output channel of the same link.

Following sucha peekorpoke,thetransputer returnstoits previouslyheld state.Any numberofaccesses

may be madein this way untilthe control byte is greaterthan 1, when the transputer willcommence read-

ing its bootstrap program. Either link can be used, but addresses and data must be transmitted via the

same link as the control byte.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425J17S | Peripheral IC |

| IMST425-J17S | 32-Bit Microprocessor |

| IMST425J20S | Peripheral IC |

| IMST425-J20S | 32-Bit Microprocessor |

| IMST425-J25S | 32-Bit Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-J25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。