- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄353712 > IS42LS16800A-7B CAP 2400UF 450V ELECT SCREW TERM PDF資料下載

參數(shù)資料

| 型號: | IS42LS16800A-7B |

| 英文描述: | CAP 2400UF 450V ELECT SCREW TERM |

| 中文描述: | 16Meg × 8,8Meg x16 |

| 文件頁數(shù): | 51/66頁 |

| 文件大?。?/td> | 556K |

| 代理商: | IS42LS16800A-7B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

55

ADVANCEDINFORMATION

Rev. 00A

06/01/02

ISSI

IS42S81600A, IS42S16800A, IS42S32400A

IS42LS81600A, IS42LS16800A, IS42LS32400A

DON'T CARE

CLK

COMMAND

BANK n

BANK m

ADDRESS

DQ

T0

T1

T2

T3

T4

T5

T6

T7

NOP

DOUT a

DOUT a+1

DOUT b

DOUT b+1

BANK n,

COL a

BANK m,

COL b

CAS Latency - 3 (BANK n)

CAS Latency - 3 (BANK m)

tRP - BANK n

tRP -BANKm

READ - AP

BANK n

READ - AP

BANK m

Page Active

READ with Burst of 4

Interrupt Burst, Precharge

Idle

Page Active

READ with Burst of 4

Precharge

Internal States

DON'T CARE

CLK

COMMAND

BANK n

BANK m

ADDRESS

DQM

DQ

T0

T1

T2

T3

T4

T5

T6

T7

NOP

DOUT a

DIN b

DIN b+1

DIN b+2

DIN b+3

BANK n,

COL a

BANK m,

COL b

CAS Latency - 3 (BANK n)

tRP - BANK n

tRP -BANKm

WRITE - AP

BANK n

WRITE - AP

BANK m

READ with Burst of 4

Interrupt Burst, Precharge

Idle

Page Active

WRITE with Burst of 4

Write-Back

Internal States

Page Active

BURST READ/SINGLE WRITE

The burst read/single write mode is entered by programming

the write burst mode bit (M9) in the mode register to a logic 1.

In this mode, all WRITE commands result in the access of a

single column location (burst of one), regardless of the

programmed burst length. READ commands access

columns according to the programmed burst length and

sequence, just as in the normal mode of operation (M9 = 0).

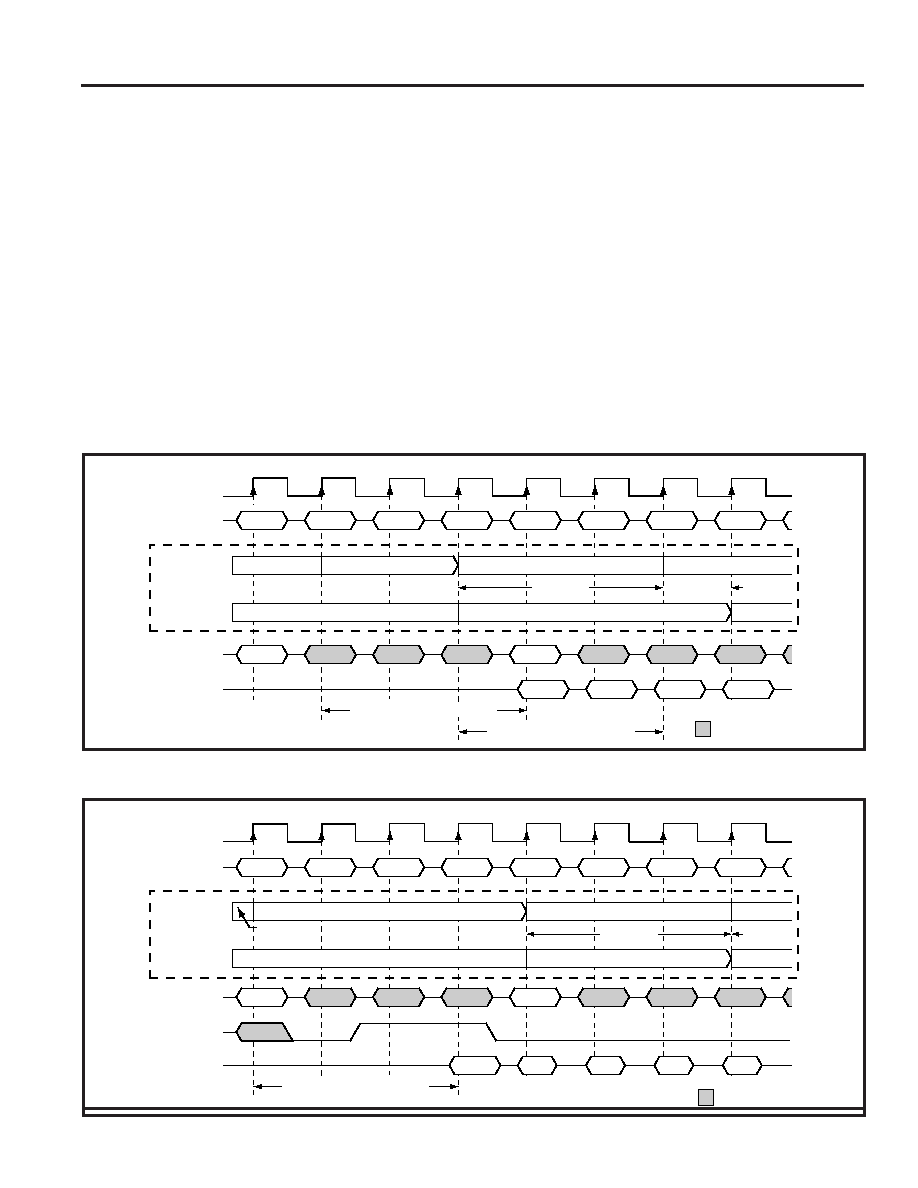

CONCURRENT AUTO PRECHARGE

An access command (READ or WRITE) to another bank

while an access command with auto precharge enabled is

executing is not allowed by SDRAMs, unless the SDRAM

supports CONCURRENT AUTO PRECHARGE. ISSI

SDRAMs support CONCURRENT AUTO PRECHARGE.

Four cases where CONCURRENT AUTO PRECHARGE

occurs are defined below.

READ with Auto Precharge

1. Interrupted by a READ (with or without auto precharge):

A READ to bank m will interrupt a READ on bank n, CAS

latency later. The PRECHARGE to bank n will begin

when the READ to bank m is registered.

2. Interrupted by a WRITE (with or without auto precharge):

A WRITE to bank m will interrupt a READ on bank n when

registered. DQM should be used two clocks prior to the

WRITE command to prevent bus contention. The

PRECHARGE to bank n will begin when the WRITE to

bank m is registered.

READ With Auto Precharge interrupted by a READ

READ With Auto Precharge interrupted by a WRITE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS42LS16800A-7BI | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS16800A-7T | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS16800A-7TI | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IC42S81600-7TI(G) | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600-8TI(G) | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS42LS16800A-7BI | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS16800A-7T | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS16800A-7TI | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS32400A | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS32400A-10B | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。