- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377572 > IS62WV6416ALL-55BLI (INTEGRATED SILICON SOLUTION INC) 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | IS62WV6416ALL-55BLI |

| 廠商: | INTEGRATED SILICON SOLUTION INC |

| 元件分類: | DRAM |

| 英文描述: | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| 中文描述: | 64K X 16 STANDARD SRAM, 55 ns, PBGA48 |

| 封裝: | 6 X 8 MM, LEAD FREE, MINI, BGA-48 |

| 文件頁(yè)數(shù): | 10/17頁(yè) |

| 文件大?。?/td> | 116K |

| 代理商: | IS62WV6416ALL-55BLI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

10

Integrated Silicon Solution, Inc. — www.issi.com —

1-800-379-4774

Rev. B

06/03/05

IS62WV6416ALL, IS62WV6416BLL

ISSI

Notes:

1. WRITE is an internally generated signal asserted during an overlap of the LOW states on the

CS1

, CS2 and

WE

inputs and at

least one of the

LB

and

UB

inputs being in the LOW state.

2. WRITE = (

CS1

) [ (

LB

) = (

UB

) ] (

WE

).

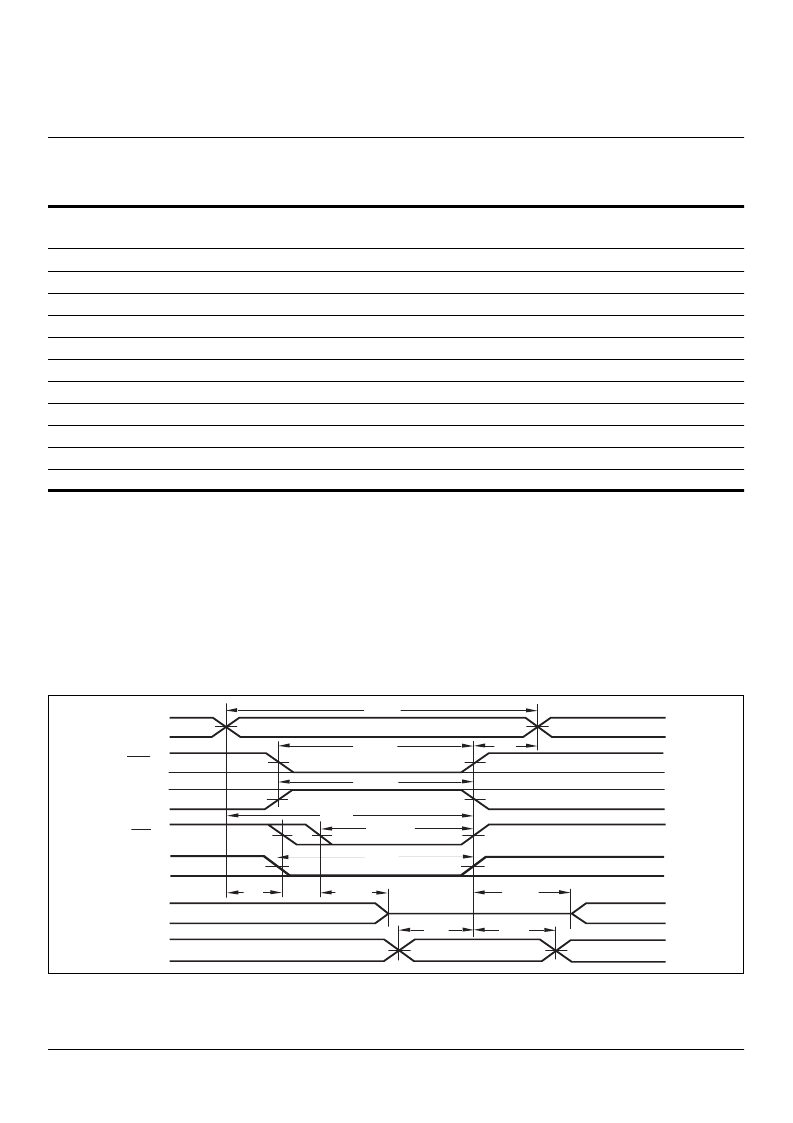

AC WAVEFORMS

WRITE CYCLE NO. 1

(1,2)

(

CS1

Controlled,

OE

= HIGH or LOW)

DATA-IN VALID

DATA UNDEFINED

t

WC

t

SCS1

t

SCS2

t

AW

t

HA

t

PWE

t

HZWE

HIGH-Z

t

LZWE

t

SA

t

SD

t

HD

ADDRESS

CS1

CS2

WE

DOUT

DIN

LB

,

UB

t

PWB

WRITE CYCLE SWITCHING CHARACTERISTICS

(1,2)

(Over Operating Range)

45ns 55 ns

Min.

Max.

45

—

35

—

35

—

0

—

0

—

35

—

35

—

20

—

0

—

—

20

5

—

Symbol

t

WC

t

SCS1/

t

SCS2

t

AW

t

HA

t

SA

t

PWB

t

PWE

t

SD

t

HD

t

HZWE

(3)

t

LZWE

(3)

Parameter

Write Cycle Time

CS1/

CS2 to Write End

Address Setup Time to Write End

Address Hold from Write End

Address Setup Time

LB

,

UB

Valid to End of Write

WE

Pulse Width

Data Setup to Write End

Data Hold from Write End

WE

LOW to High-Z Output

WE

HIGH to Low-Z Output

Min.

55

45

45

0

0

45

40

25

0

—

5

Max.

—

—

—

—

—

—

—

—

—

20

—

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes:

1. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4V to

V

DD

-0.2V/V

DD

-0.3V and output loading specified in Figure 1.

2. The internal write time is defined by the overlap of

CS1

LOW, CS2 HIGH and

UB

or

LB

, and

WE

LOW. All signals must be in

valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are

referenced to the rising or falling edge of the signal that terminates the write.

3. Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS62WV6416ALL-55T | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416ALL-55TI | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416ALL-55TLI | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416BLL | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416BLL-45B | 64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS62WV6416ALL-55BLI-TR | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1M (64Kx16) 55ns Async 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| IS62WV6416ALL-55T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416ALL-55TI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416ALL-55TLI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

| IS62WV6416BLL | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:64K x 16 LOW VOLTAGE, ULTRA LOW POWER CMOS STATIC RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。