- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373060 > K4C89083AF-GIF5 (SAMSUNG SEMICONDUCTOR CO. LTD.) 288Mb x18 Network-DRAM2 Specification PDF資料下載

參數(shù)資料

| 型號: | K4C89083AF-GIF5 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 288Mb x18 Network-DRAM2 Specification |

| 中文描述: | 288Mb x18網(wǎng)絡(luò)DRAM2規(guī)范 |

| 文件頁數(shù): | 48/55頁 |

| 文件大小: | 1470K |

| 代理商: | K4C89083AF-GIF5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

K4C89183AF

- 48 -

REV. 0.7 Jan. 2005

Function Description

Network - DRAM

Network - DRAM is an acronym of Double Data Rate Network - DRAM.

Network - DRAM is competent to perform fast random core access, low latency and high-speed data transfer.

Pin Functions

Clock Inputs : CLK & CLK

The CLK and CLK inputs are used as the reference for synchronous operation. CLK is master clock input. The CS, FN and all

address input signals are sampled on the crossing of the positive edge of CLK and the negative edge of CLK. The QS and DQ output

data are aligned to the crossing point of CLK and CLK. The timing reference point for the differential clock is when the CLK and CLK

signals cross during a transition.

Power Down : PD

The PD input controls the entry to the Power Down or Self-Refresh modes. The PD input does not have a Clock Suspend function like

a CKE input of a standard SDRAMs, therefore it is illegal to bring PD pin into low state if any Read or Write operation is being per-

formed.

Chip Select & Function Control : CS & FN

The CS and FN inputs are a control signal for forming the operation commands on Network-DRAM. Each operation mode is decided

by the combination of the two consecutive operation commands using the CS and FN inputs.

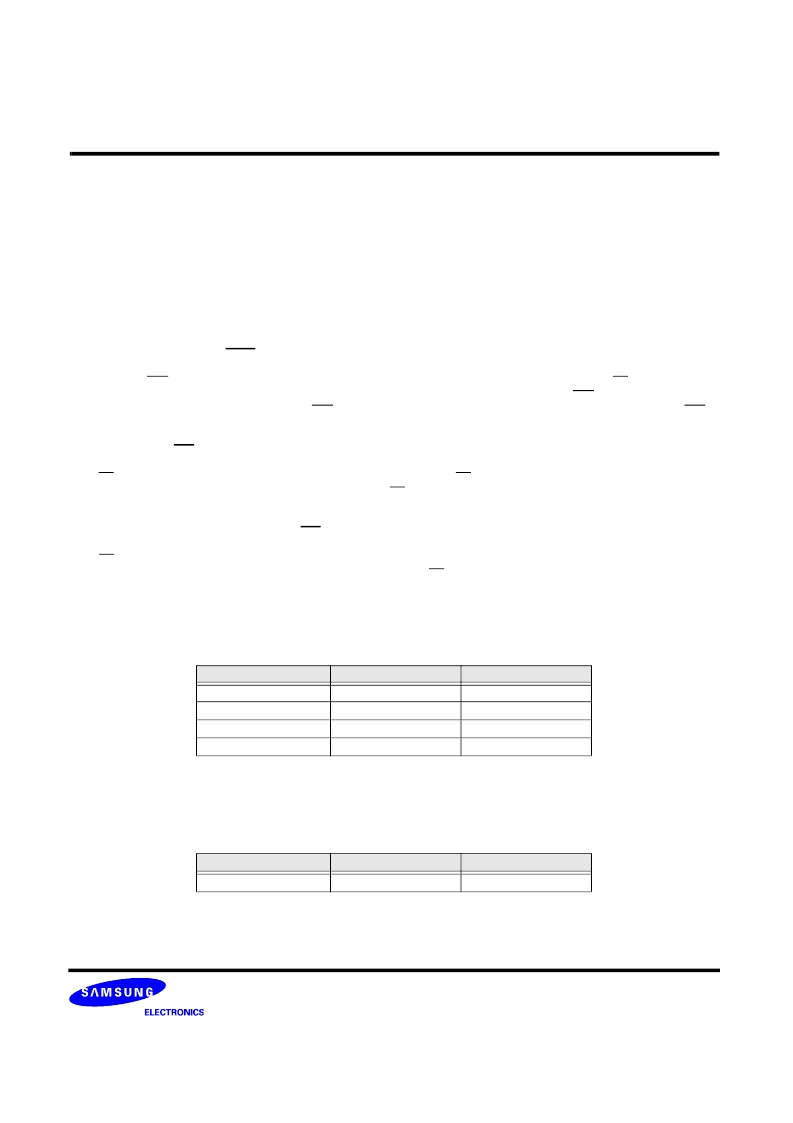

Bank Addresses : BA0 & BA1

The BA0 and BA1 inputs are latched at the time of assertion of the RDA or WRA command and are selected the bank to be used for

the operation. BA0 and BA1 also define which mode register is loaded during the Mode Register Set command (MRS or EMRS).

Address Inputs : A0 to A14

Address inputs are used to access the arbitrary address of the memory cell array within each bank. The Upper Addresses with Bank

address are latched at the RDA or WRA command and the Lower Addresses are latched at the LAL command. The A0 to A14 inputs

are also used for setting the data in the Regular or Extended Mode Register set cycle.

BA0

BA1

Bank #0

Bank #1

0

1

0

0

Bank #2

0

1

Bank #3

1

1

Upper Address

A0 to A14

Lower Address

A0 to A6

K4C89183AF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4C89083AF-GIF6 | 288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACF5 | 288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACF6 | 288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACFB | 288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-AIF5 | 288Mb x18 Network-DRAM2 Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4C89083AF-GIF6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:288Mb x18 Network-DRAM2 Specification |

| K4C89083AF-GIFB | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACF5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACF6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:288Mb x18 Network-DRAM2 Specification |

| K4C89093AF-ACFB | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:288Mb x18 Network-DRAM2 Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。