- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358024 > K4S64323LH-FC75 (SAMSUNG SEMICONDUCTOR CO. LTD.) 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | K4S64323LH-FC75 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| 中文描述: | 為512k × 32Bit的× 4銀行在90FBGA移動(dòng)SDRAM |

| 文件頁(yè)數(shù): | 8/8頁(yè) |

| 文件大小: | 64K |

| 代理商: | K4S64323LH-FC75 |

K4S64323LF-S(D)N/U/P

Rev. 1.5 Dec 2002

CMOS SDRAM

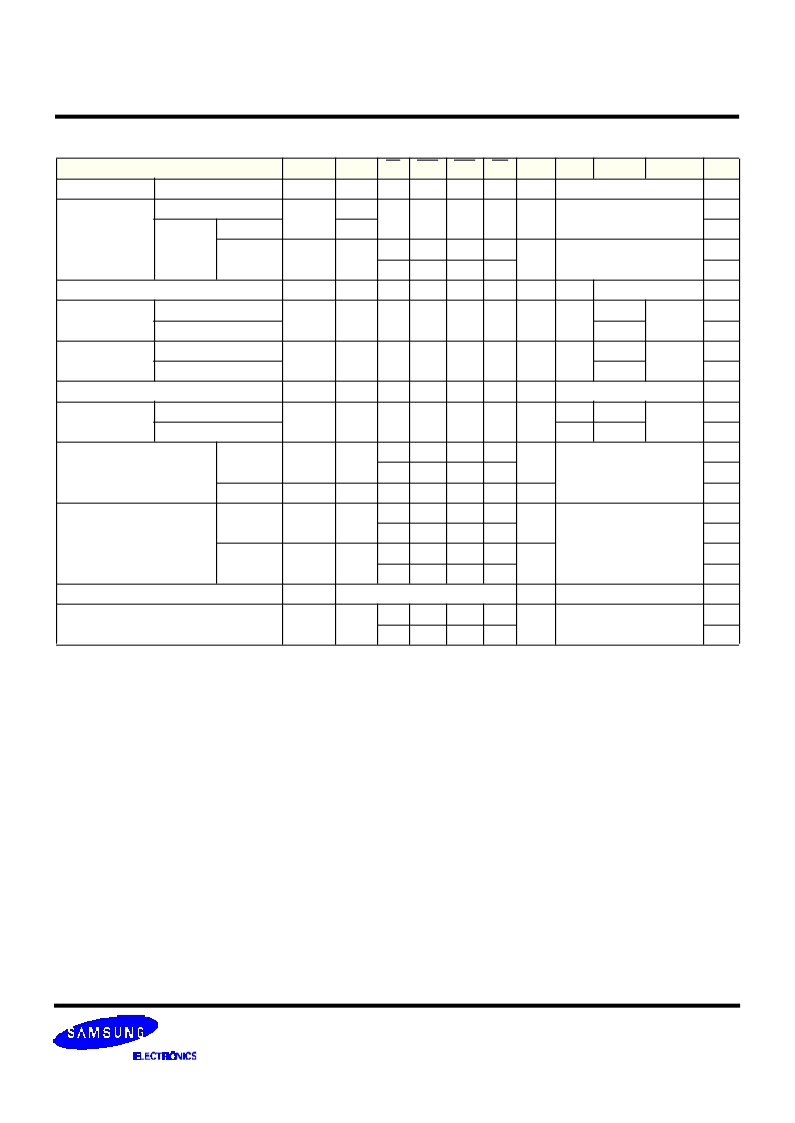

SIMPLIFIED TRUTH TABLE

(V=Valid, X=Don

′

t Care, H=Logic High, L=Logic Low)

Note :

1. OP Code : Operand Code

A

0

~ A

10

& BA

0

~ BA

1

: Program keys. (@MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are the same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA

0

~ BA

1

: Bank select addresses.

If both BA

0

and BA

1

are "Low" at read, write, row active and precharge, bank A is selected.

If BA

0

is "Low" and BA

1

is "High" at read, write, row active and precharge, bank B is selected.

If BA

0

is "High" and BA

1

is "Low" at read, write, row active and precharge, bank C is selected.

If both BA

0

and BA

1

are "High" at read, write, row active and precharge, bank D is selected.

If A

10

/AP is "High" at row precharge, BA

0

and BA

1

are ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at t

RP

after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at the positive going edge of CLK masks the data-in at that same CLK in write operation (Write DQM latency

is 0), but in read operation it makes the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2).

COMMAND

CKEn-1

CKEn

CS

RAS

CAS

WE

DQM

BA

0,1

A

10

/AP

A

9

~ A

0

Note

Register

Mode Register Set

H

X

L

L

L

L

X

OP CODE

1, 2

Refresh

Auto Refresh

H

H

L

L

L

H

X

X

3

Self

Refresh

Entry

L

3

Exit

L

H

L

H

H

H

X

X

3

H

X

X

X

3

Bank Active & Row Addr.

H

X

L

L

H

H

X

V

Row Address

Read &

Column Address

Auto Precharge Disable

H

X

L

H

L

H

X

V

L

Column

Address

(A

0

~A

7

)

4

Auto Precharge Enable

H

4, 5

Write &

Column Address

Auto Precharge Disable

H

X

L

H

L

L

X

V

L

Column

Address

(A

0

~A

7

)

4

Auto Precharge Enable

H

4, 5

Burst Stop

H

X

L

H

H

L

X

X

6

Precharge

Bank Selection

H

X

L

L

H

L

X

V

L

X

All Banks

X

H

Clock Suspend or

Active Power Down

Entry

H

L

H

X

X

X

X

X

L

V

V

V

Exit

L

H

X

X

X

X

X

Precharge Power Down Mode

Entry

H

L

H

X

X

X

X

X

L

H

H

H

Exit

L

H

H

X

X

X

X

L

V

V

V

DQM

H

X

V

X

7

No Operation Command

H

X

H

X

X

X

X

X

L

H

H

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4S64323LH-FE1H | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE1L | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE60 | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE75 | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FF1H | 512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4S64323LH-FE1H | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE1L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FE75 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

| K4S64323LH-FF1H | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 32Bit x 4 Banks Mobile SDRAM in 90FBGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。